2022. 3. 15. 16:10ㆍ강의 내용 정리/컴퓨터구조

Combinational Logical Circuits and Design

1. Building blocks of modern computers

(1) Transistors

- 컴퓨터는 매우 간단한 스트럭쳐인 트랜지스터가 매우 많이 들어가있다.

ex) 2000년에 판매된 Intel's Pentium IV 마이크로 프로세서는 42milion MOS 트랜지스터가 있었는데 2016년에 판매된 i7은 3.2bilion MOS 트랜지스터가 사용됨

MOS 트랜지스터

- Conductors(Metal), Insulators(Oxide), Semiconductors로 구성되어있음

- 간단한 로직게이트를 MOS 트랜지스터를 사용해 구현할 수 있기에 유명함

- MOS 트랜지스터의 두 가지 유형

* n-type: 특정 voltage 이상을 주면 연결이 됨

* p-type: 특정 voltage 이상을 주면 연결이 안됨

- 최근 컴퓨터는 n-type과 p-type 트랜지스터를 둘 다 사용하는데 이를 Complementary MOS(CMOS) 기술이라 함

- nMOS + pMOS = CMOS

(2) Logic gates

CMOS NOT gate

- 0V입력 -> 3V출력 / 3V입력 -> 0V출력이 됨

- inverter의 역할을 하는 게이트

CMOS NAND gate

- P1과 P2가 병렬로 연결되어있기에 하나만 ON이면 output이 3V임

- N1과 N2가 직렬로 연결되어있기에 둘 다 ON이어야지 output이 0V임

CMOS AND gate

- NAND gate의 output을 NOT gate의 입력과 연결함

CMOS gate structure

- 트랜지스터가 병렬로 연결되어있으면 둘 중 하나만 ON이어도 결과가 ON임

- 트랜지스터가 직렬로 연결되어있으면 둘 다 ON이어야지 결과가 ON임

- pMOS 트랜지스터는 pull-up할 때 사용

- nMOS 트랜지스터는 pull-down할 때 사용

Latency

- 트랜지스터를 병렬로 연결하는 것이 더 빠름

Power consumption

- Dynamic Power Consumption: Capacitance of the circuit x Supply voltage^2 x charging frerquency of the capacitor

- Static power consumption: supply voltage x leakage current

- Energy consumption: Power x Time

무어의 법칙

- 2년 동안 트랜지스터의 개수가 약 2배 이상 많아진다.

- 더 작은 트랜지스터와 구조를 만들고 더 나은 properties의 materials를 개발해서 무어의 법칙을 지켜내고자함

Logic circuits

- Functional specification: 인풋과 아웃풋의 관계 명시 / 동일한 입력에 대해선 동일한 출력이 나와야함

- Timing specification: 인풋이 변화되는 시간부터 아웃풋의 반응시간 사이의 딜레이를 명시

Combinational Logic

- 메모리가 없고, 입력에 따라서 출력이 달라짐

Sequential Logic

- 메모리가 존재하고, 입력과 메모리에 저장된 값을 토대로 출력이 달라짐

2. Boolean algebra

- Axiom(공리)에서부터 시작해서 AND, OR, NOT 연산을 해 1, 0 등의 값을 출력함

Duality

- 모든 AND 연산은 OR 연산으로 표현이 가능하고 모든 OR 연산은 AND 연산으로 표현 가능함

- 모든 상수 1은 0으로 표현할 수 있고, 모든 상수 0은 1로 표현할 수 있다.

드모르간의 법칙

- input 보수들의 OR는 NAND와 동일

- input 보수들의 AND는 NOR와 동일

3. combinational circuits

- 위의 게이트를 활용해 더 복잡한 게이트를 만들 수 있음

- 인풋이 동일한 경우 아웃풋도 동일하게 나와야함 -> 이때 메모리는 없는 조합회로를 의미함

조합회로와 관련된 개념

Minterm: 모든 인풋 변수의 곱(AND)으로 이루어진 경우

Maxterm: 모든 인풋 변수의 합(OR)으로 이루어진 경우

Sum Of Products(SOP): 인풋의 조합 중 하나라도 1이라면 아웃풋도 1이 됨

Products Of Sum(POS): 드모르간의 법칙을 활용해 인풋의 조합 중 0이 되는 조합에 모두 보수화를 하면 표현가능

Shorthand notation: canonical forms에서 변수를 모두 작성하는 경우 너무 길기에 이를 숫자로 줄여서 표현하는 방식

4. Combinational building blocks used in modern computers

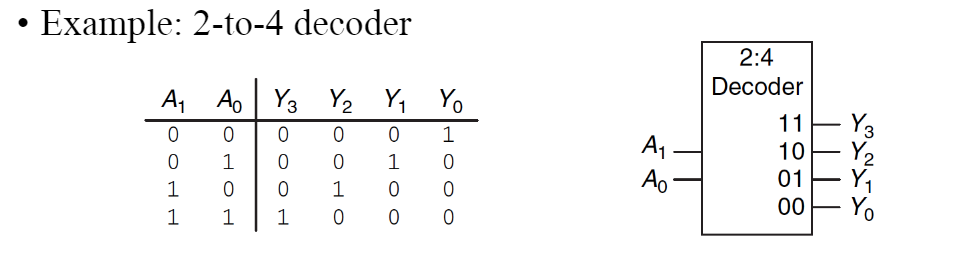

(1) Decoder

- input 패턴을 검출하는 역할

- n개의 input이 있으면 2^n개의 아웃풋이 존재

- 주소에서 많이 사용됨

(2) Multiplexer(MUX)

- 여러개 중 하나를 선택해서 동작하게끔 할 때 필요한 모듈

- N개의 입력 중 하나를 선택해서 output으로 보내줄 때 이를 Multiplexer라고 함

-> S에 어떤 신호를 주느냐에 따라 출력 값이 달라짐

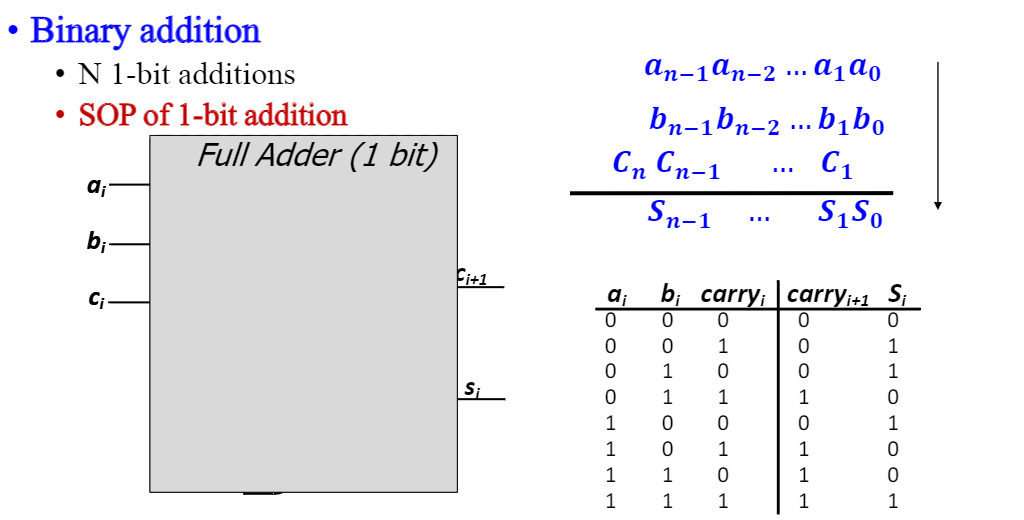

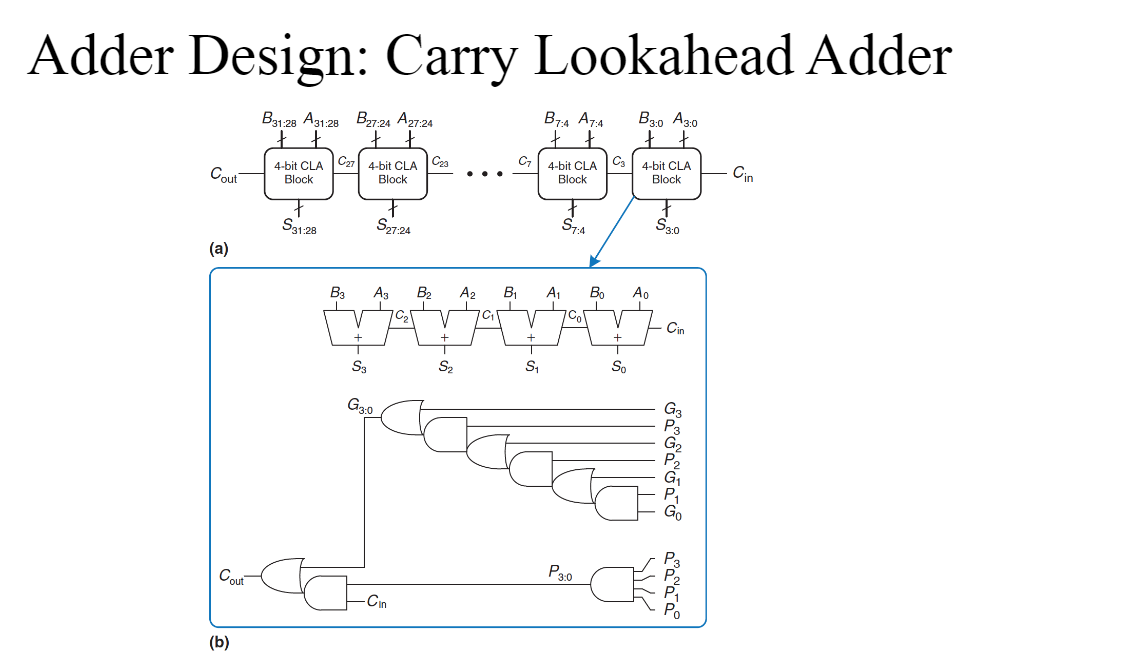

(3) Full adder

- 이진 덧셈기로서 자리수를 나타내는 carry와 덧셈의 결과인 sum을 출력한다.

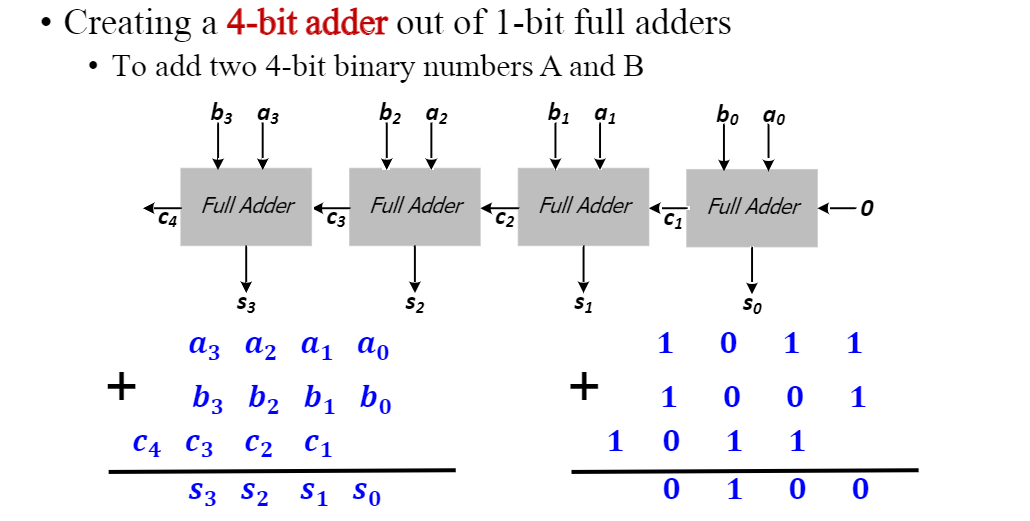

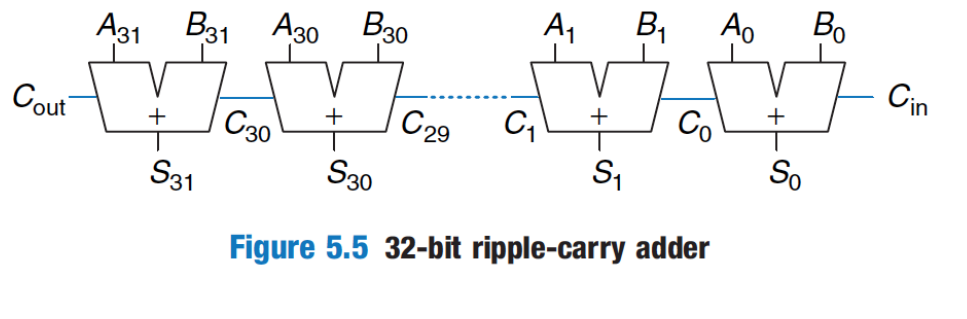

- Full adder의 결합을 통해 여러 비트의 adder를 만들 수 있다.

- 위와 같은 adder는 이전 자리수의 carry를 받아야지 연산이 가능하기에 비트수가 많아질수록 더 오랜 시간이 걸린다.

-> 이에 따라 아래와 같은 다른 adder를 사용하기도 함

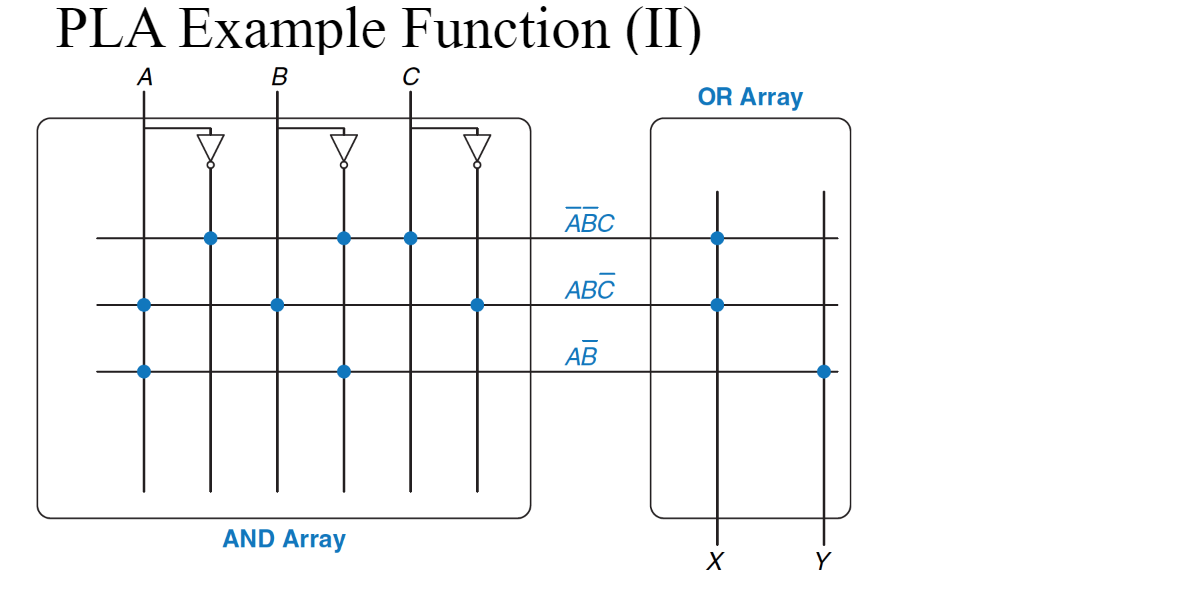

(4) Programmable Logic Array(PLA)

- AND Array와 OR Array의 결합으로 구현

- Flexable하게 우리가 원하는 기능을 만들 수 있는 form

- AND 게이트의 숫자는 가능한 minterm의 숫자만큼이 됨

Logical completeness

- 여태 배운 blocks들과 게이트를 통해 무엇이든지 논리적으로 completeness하게 구현할 수 있음

(5) 그 외의 다양한 blocks

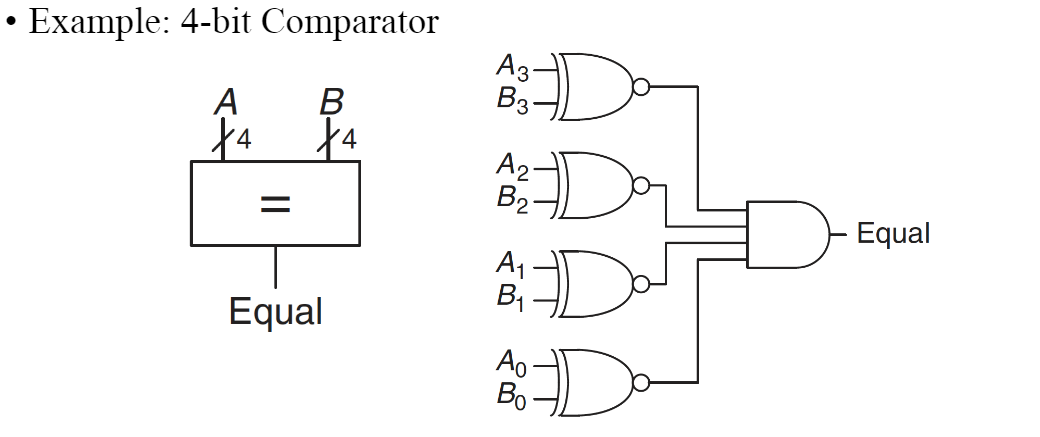

Equality checker

- 입력의 비트수를 각각 비교해서 같은지 확인하는 checker

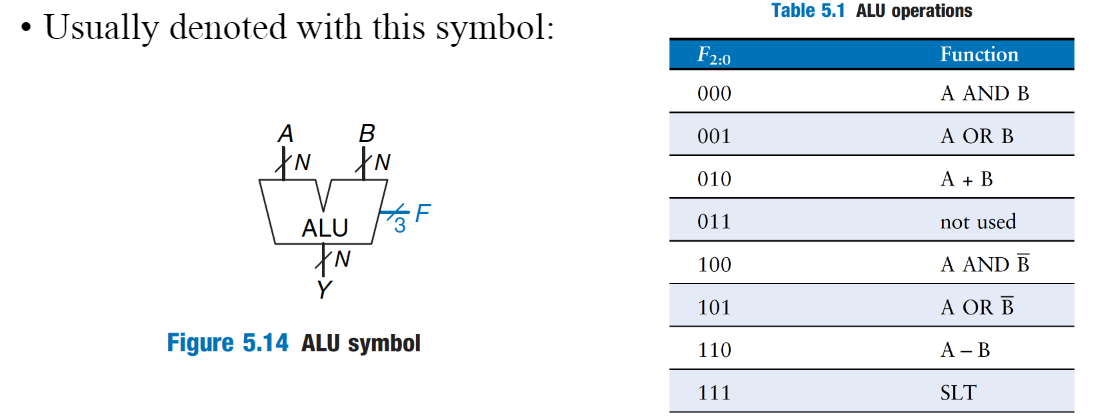

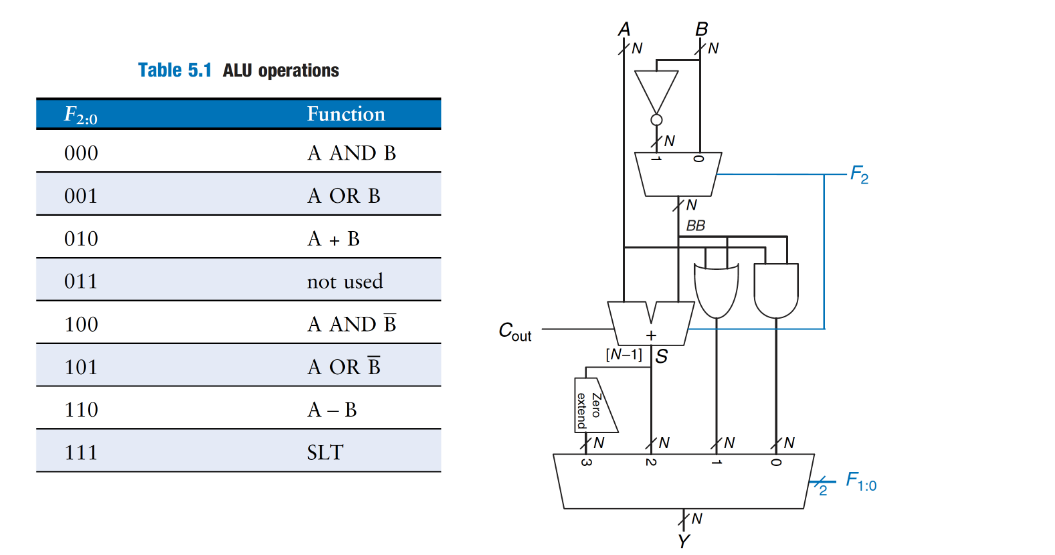

ALU(Arithmetic Logic Unit)

- n bit의 숫자가 들어오면 control signal에 따라 연산을 진행함

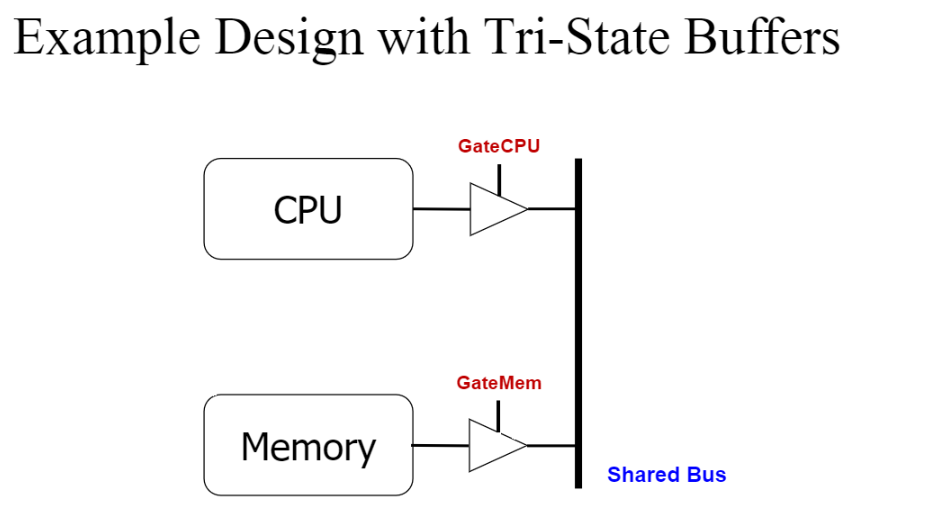

Tri-State Buffer

- 끊어진 것에 대한 기능을 하는 버퍼

- CPU와 메모리를 와이어로 연결했을 때 두 군데를 동시에 처리하지 못하고 둘 중 하나만 처리하게끔 할 때 사용

- 해당 예시는 MUX로도 구현할 수 있음

- Logic Simplification은 로직을 간단하게 하기 위해 필요함

'강의 내용 정리 > 컴퓨터구조' 카테고리의 다른 글

| 컴퓨터 구조 (7), Pipelining (0) | 2022.05.23 |

|---|---|

| 컴퓨터 구조 (6), Single-cycle MIPS processor (0) | 2022.04.28 |

| 컴퓨터 구조 (5), Instruction Set Architecture 02 (0) | 2022.04.21 |

| 컴퓨터 구조 (3), Sequential Logic Circuits and Design (0) | 2022.03.22 |

| 컴퓨터 구조 (1) Computer Organization & Performance (0) | 2022.03.10 |