2022. 4. 28. 02:52ㆍ강의 내용 정리/컴퓨터구조

Single-cycle MIPS processor

- 모든 명령어가 한 사이클에서 패칭부터 동작을 다 하는 것을 의미해 single cycle이라고 한다.

Instruction fetching

하버드 아키텍쳐: 명령어 메모리와 데이터를 로드하는 메모리를 분리해서 사용하는 것

- 분리되어있는 경우가 이해하기 쉽고, 구현하기도 쉽다.

- 합쳐서 사용하는 경우에는 폰노이만 아키텍쳐이다.

CPU는 무한히 반복되는 loop로 본다.

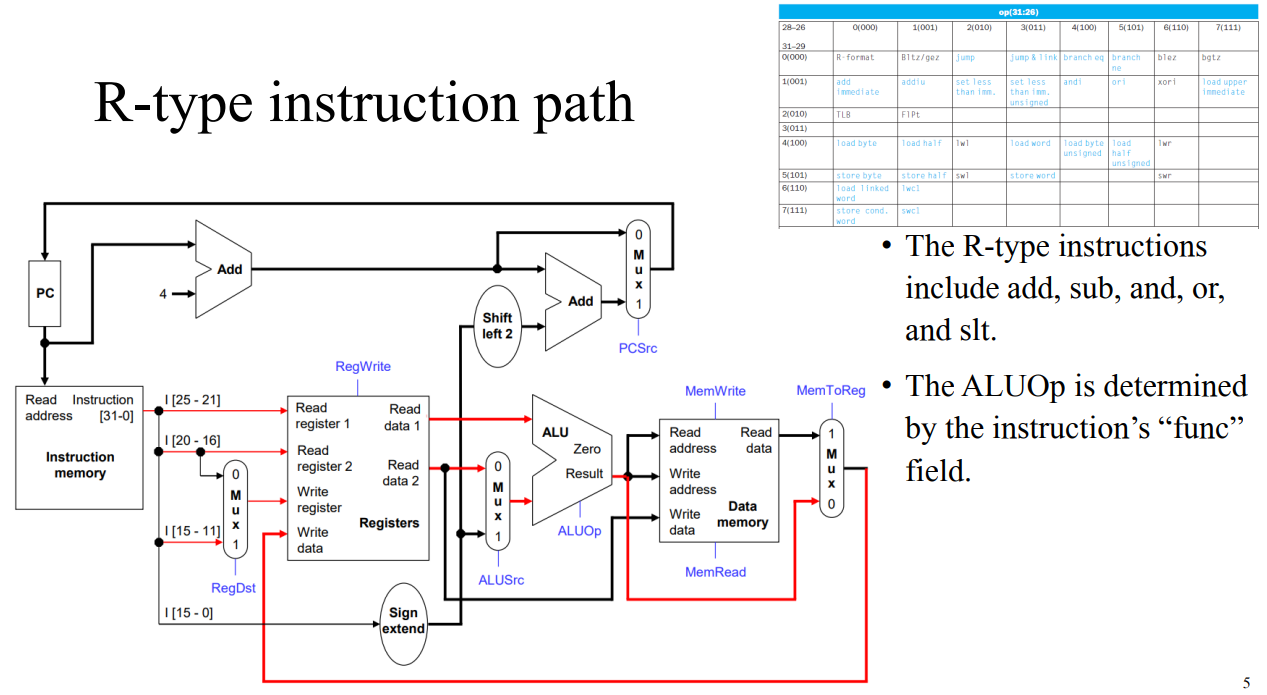

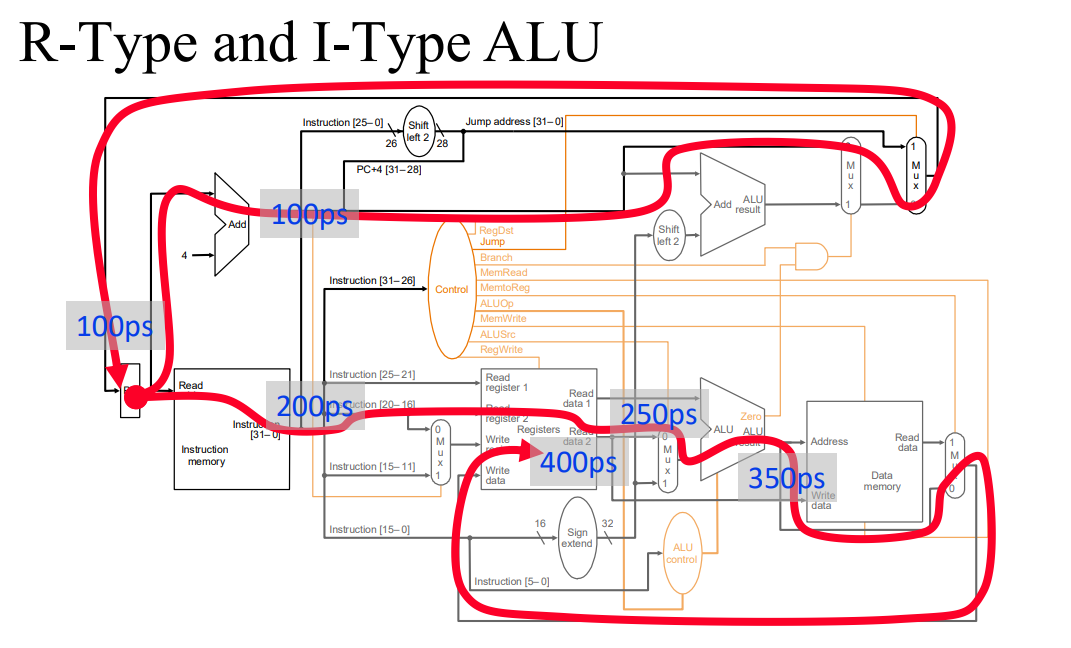

R-type 명령어

- 어떤 instruction인지 알아야지 동작한다.

- 오른쪽에 있는 내용이 register file이다.

R-type 명령어가 들어왔을 때 동작

- PC값이 들어오면 명령에서 따라서 각각 레지스터별로 들어가고 RegWrite를 거친 뒤, ALU에서 특정 연산을 걸쳐 Write data에 들어간다.

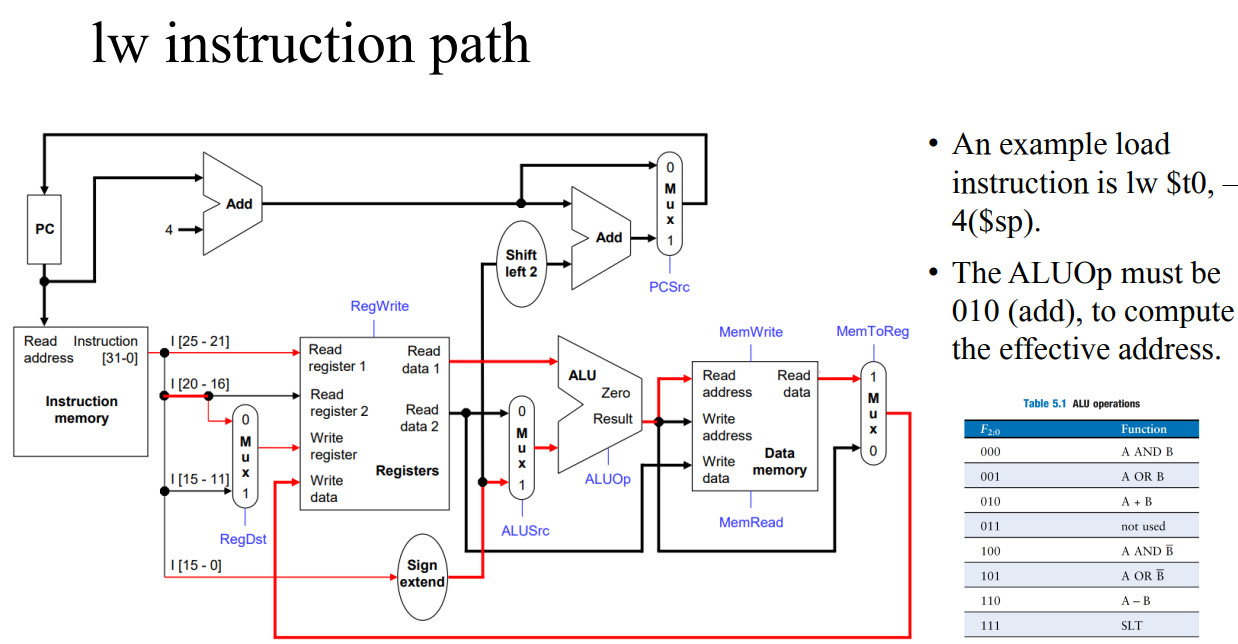

I-type 명령어

- R-type과 다른 점은 rt이 destination을 의미하기에 write register로 간다.

- RegDst는 MUX로 구현해서 write할 선을 정할 수 있다.

- sign extend에서는 address의 맨 앞에 있는 숫자를 16개만큼 만들면 32비트가 된다.

- data memory는 메모리에서 어떤 값을 저장하거나 불러오는 스토리지이다.

구체적으로 MemToRag는 다음과 같이 동작한다.

- MemToReg에서는 MUX가 있는 이유

- 데이터가 어떻게 흘러가고 그 때의 컨트롤 시그널이 어떻게 될 것인가를 집중해서 파악하는 것이 중요하다.

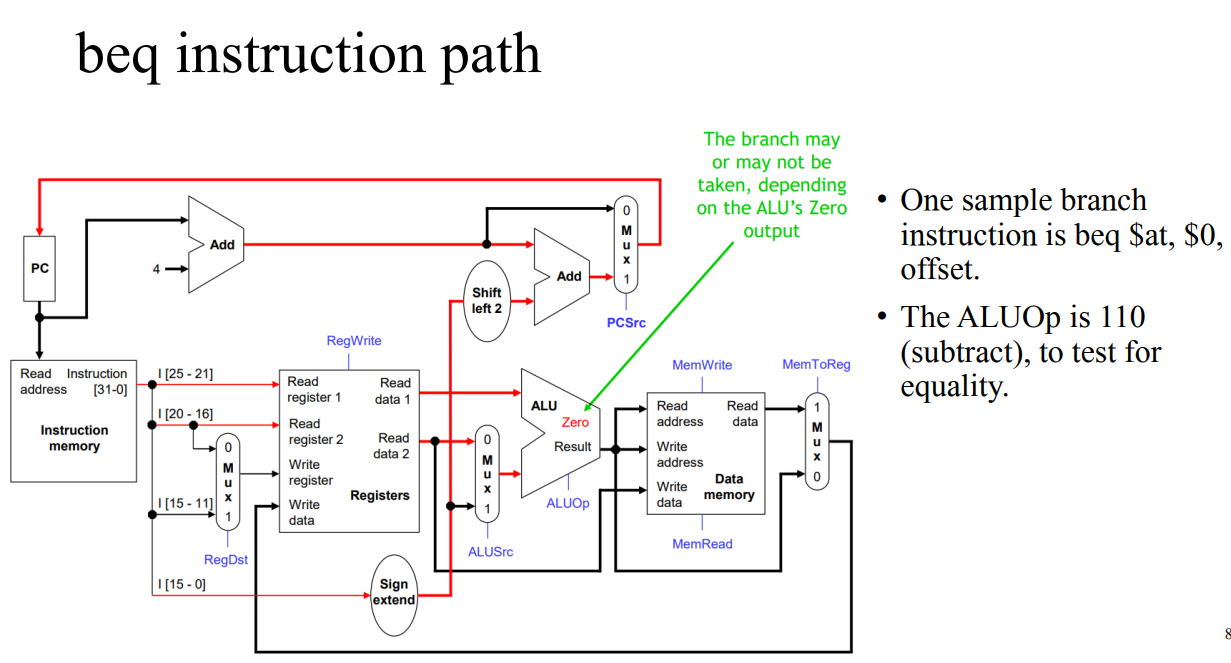

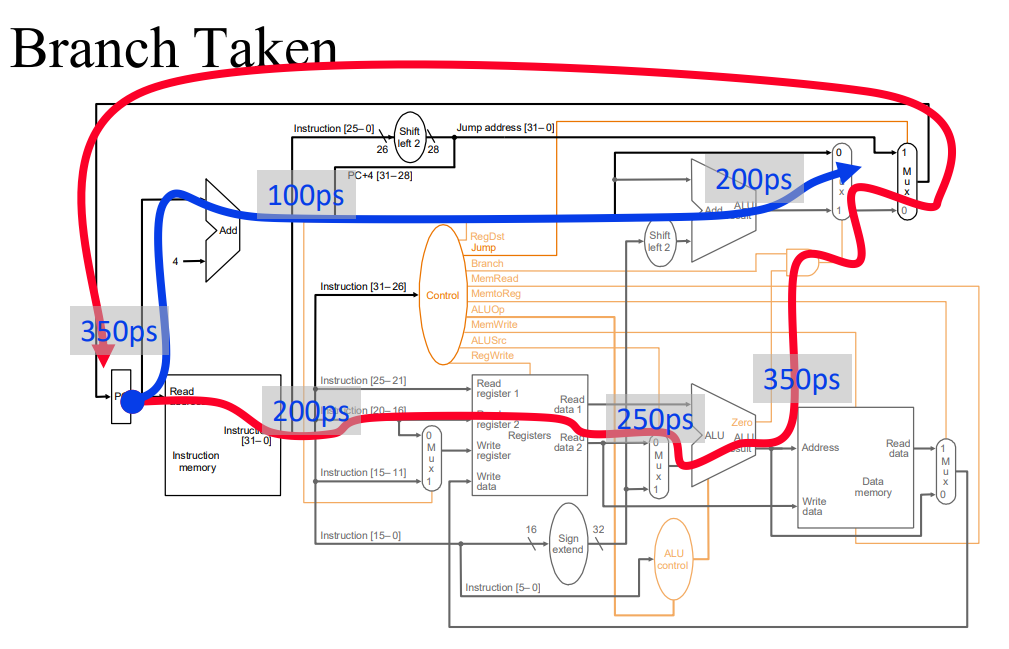

at가 0이면 L로 가라~

3줄만큼 뒤로 이동해야하기 때문에 실제 주소로 따지면 12만큼 이동해야하지만 pc값은 4가 디폴트이기에 address를 3으로 적어서 더 많은 값을 표현한다.

구체적으로 아래와 같은 동작을 진행한다.

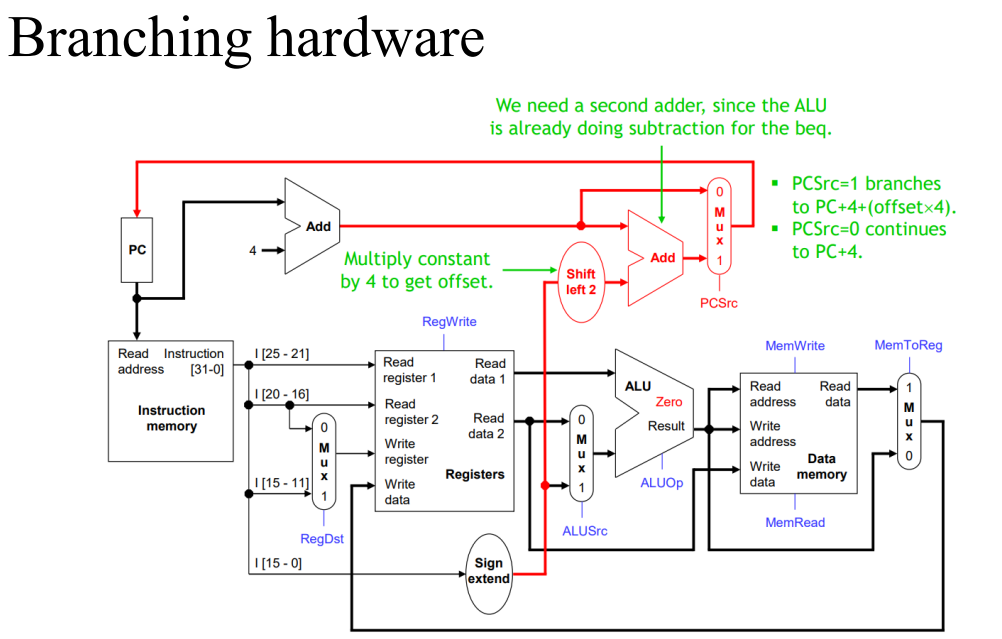

위의 동작을 구현하기 위해 하드웨어는 다음과 같은 구조를 가진다.

Branch를 하기위해선 ALUSrc의 컨트롤이 0이어야한다.

- 같지 않은 경우에는 4를 더해준다.

- ALU가 zero인지 아닌지 확인해 branch도 0이라면 branch하게끔 한다.

- branch인 경우에는 memwrite와 memread는 0인게 더 효율적이다. memtoreg에서는 0과 1 모두 상관 없다.

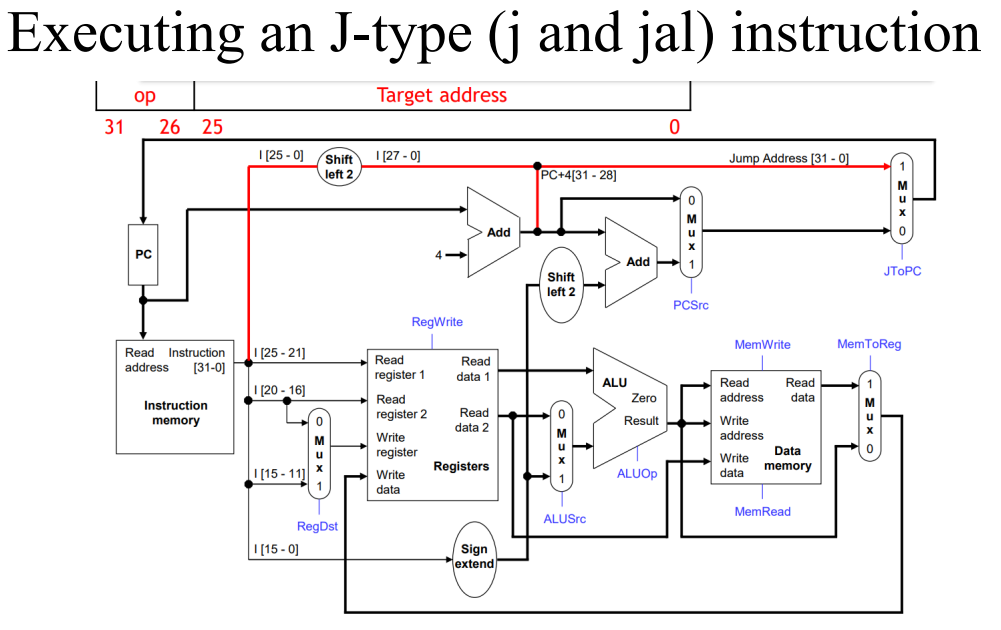

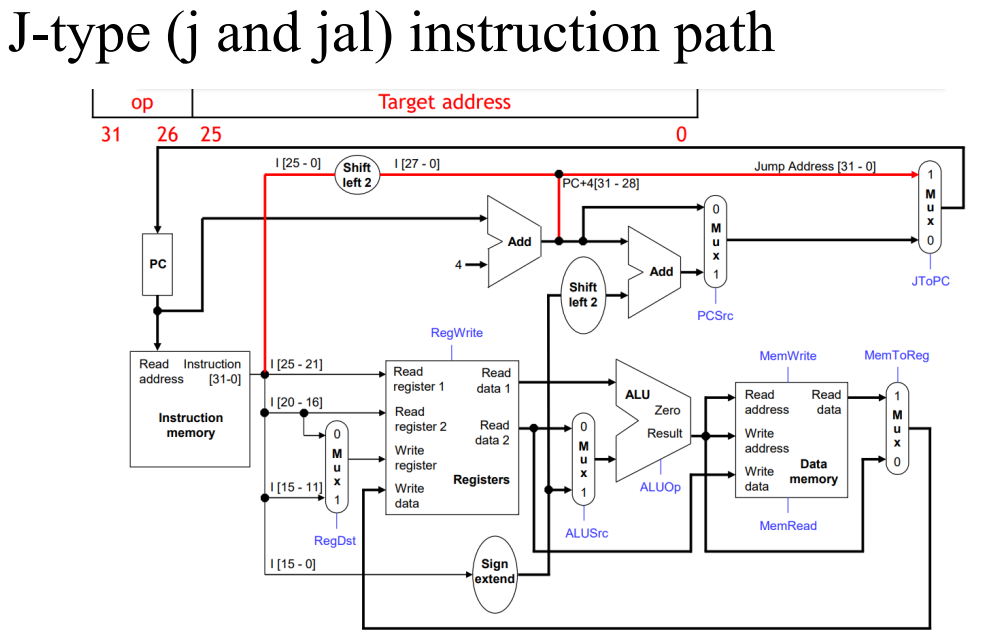

J-type

- 표현하고 싶은 것들을 잘 동작하게끔 구현하는 것이 중요함

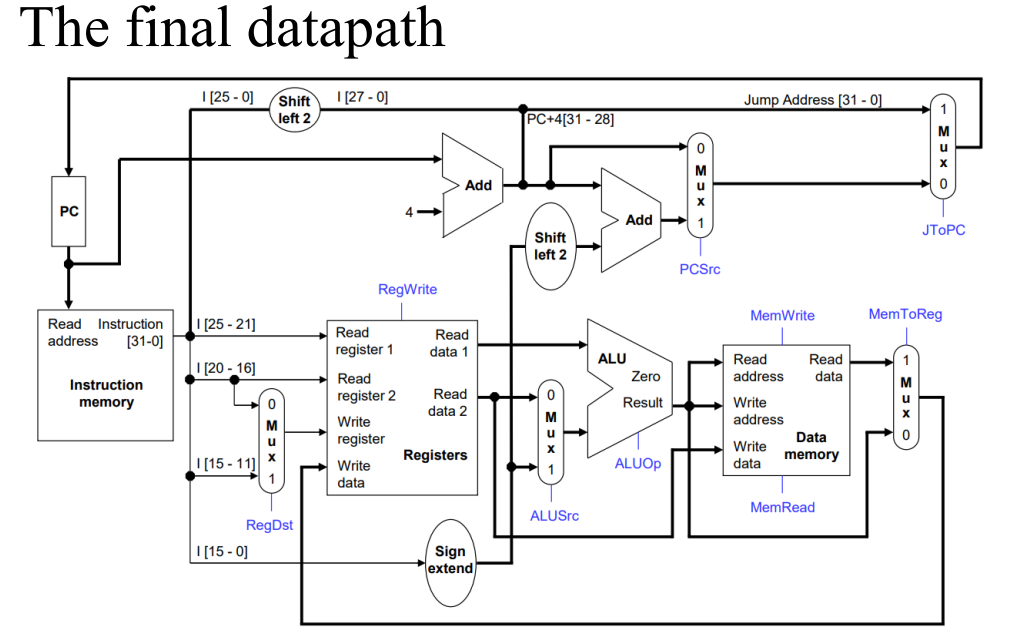

- 파란색이 컨트롤 시그널이고, 각각의 instruction에 대해 특정한 동작을 하게끔한다.

R 타입에서는 function code를 보고 ALU가 결정된다.

PCSrc는 0이다.

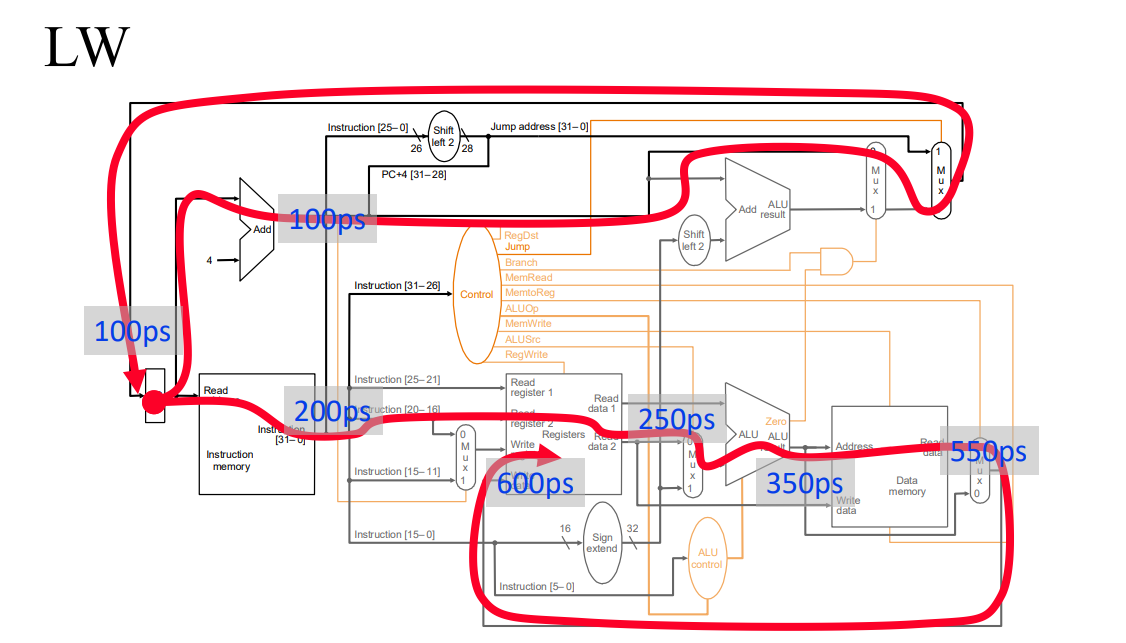

값을 로드할 때

컨트롤 시그널

- RegDst는 0이 되어야한다.

- 32비트로 만들어야하기에 ALUSrc는 1이 되어야한다.

- ALUOp에서는 덧셈과 관련된 op 시그널이 보내져야한다.

- MemWrite은 1, MemRead는 0, MemtoReg는 1, RegWrite은 1이 되어야한다.

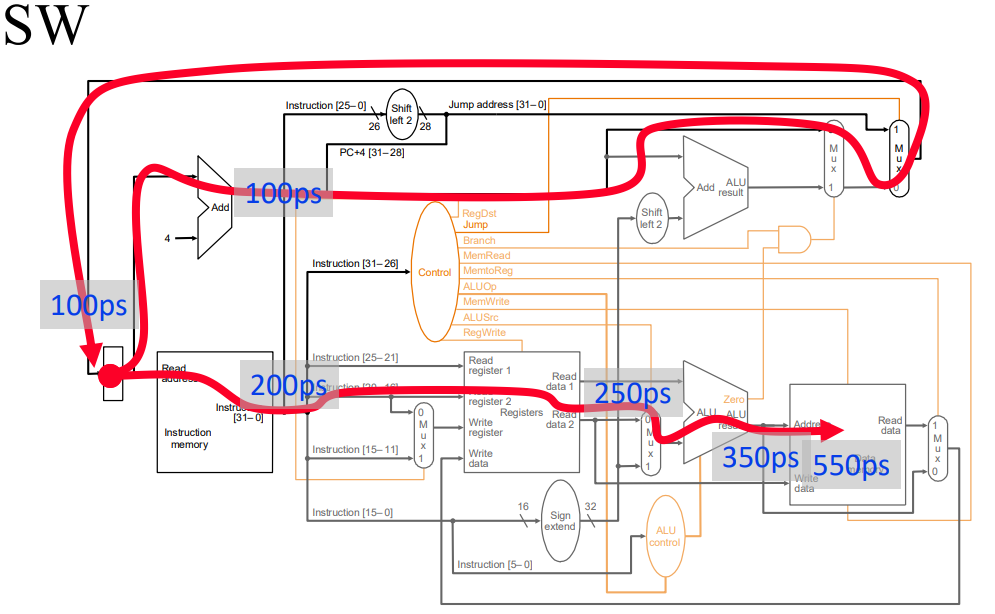

값을 저장할 때

RegWrite는 0이어야한다.

MemToReg는 어떤 값이든지 상관없다.

- 직접 해보기

- 각 상황에 따른 컨트롤 시그널을 파악! -> 시험 문제 나옴

- ALUsrc는 0이 됨

- 두 값이 같을 때 zero가 나와 1이 되도록 한다. 이에 따라 PCSrc는 1이된다. -> Branch가 아닌 경우에는 다 0의 값을 가졌다.

- RegWrite, MemWrite, MemRead는 0이 되어야한다. 사실 MemRead는 상관없지만 1의 값을 주면 다소 비효율적이게 동작할 수 있기 때문

- MemToReg, RegDst는 상관없다.

J-type의 경우

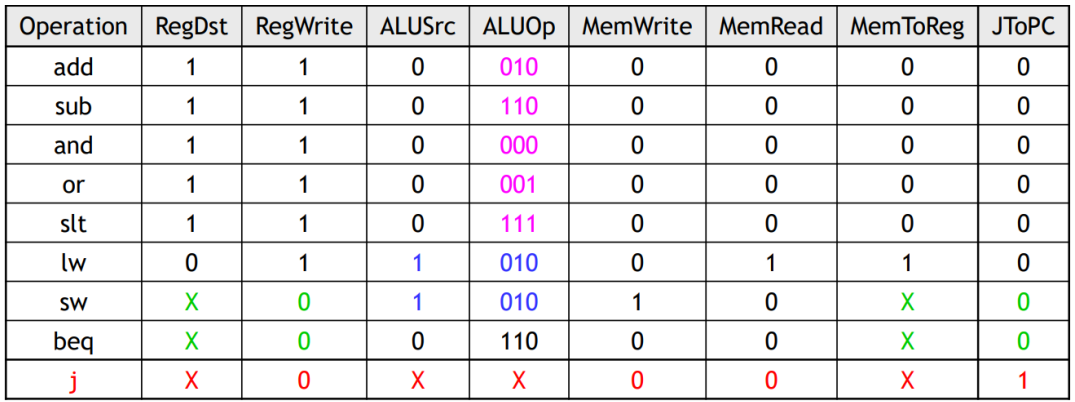

Control signal table

- JToPC는 점프냐 아니냐를 따지는 것이기에 jump에서만 1이다.

- sw, beq는 레지스터에 쓰지 않는 명령어이고 ALU에서는

- PCSrc는 테이블이 없지만 beq와 ALU의 zero 아웃풋이 true일 때 1이다.

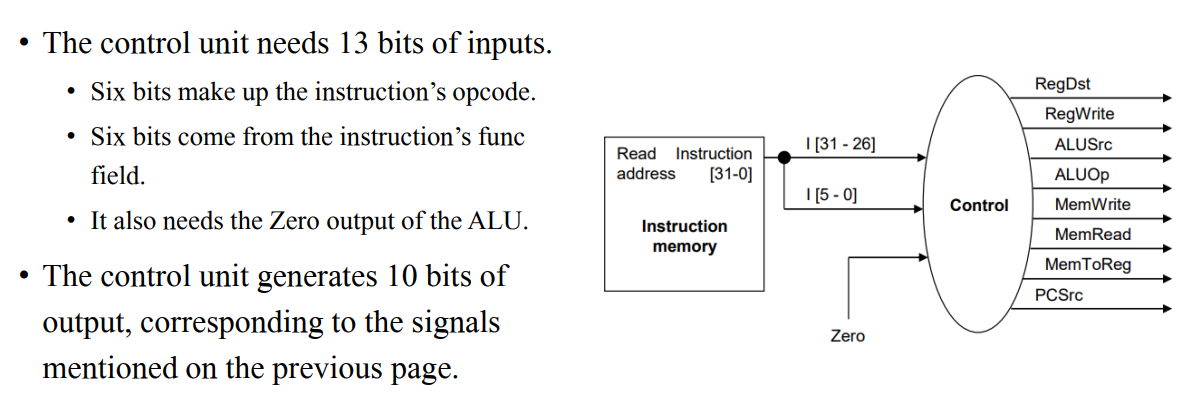

Generating control signals

- 컨트롤 유닛에 13비트 입력이 들어오게 되고 출력은 11개가 나온다. 컨트롤 시그널은 9개이지만 출력은 11개가 나온다. -> JToPc까지 포함해야함

- 13개의 인풋 중 op코드는 13개이다.

- 블럭단위로 구현한 control

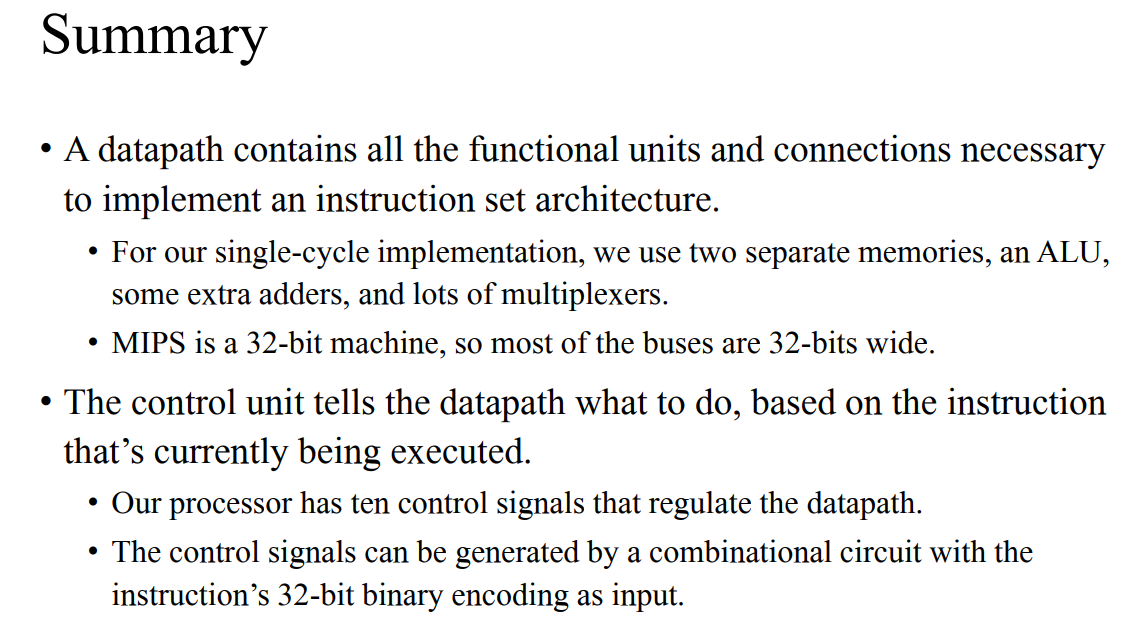

정리

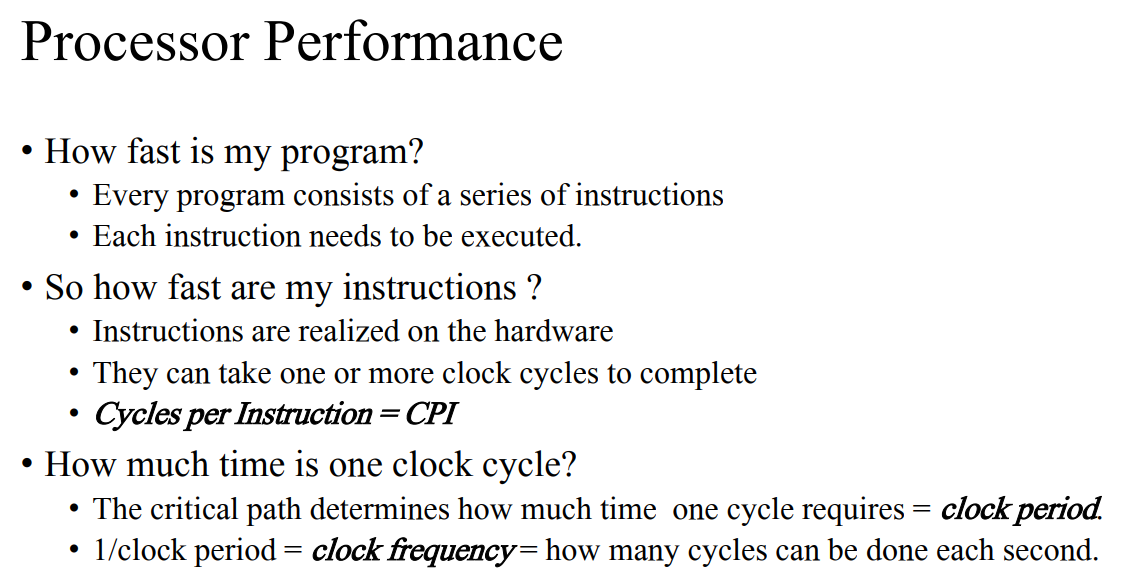

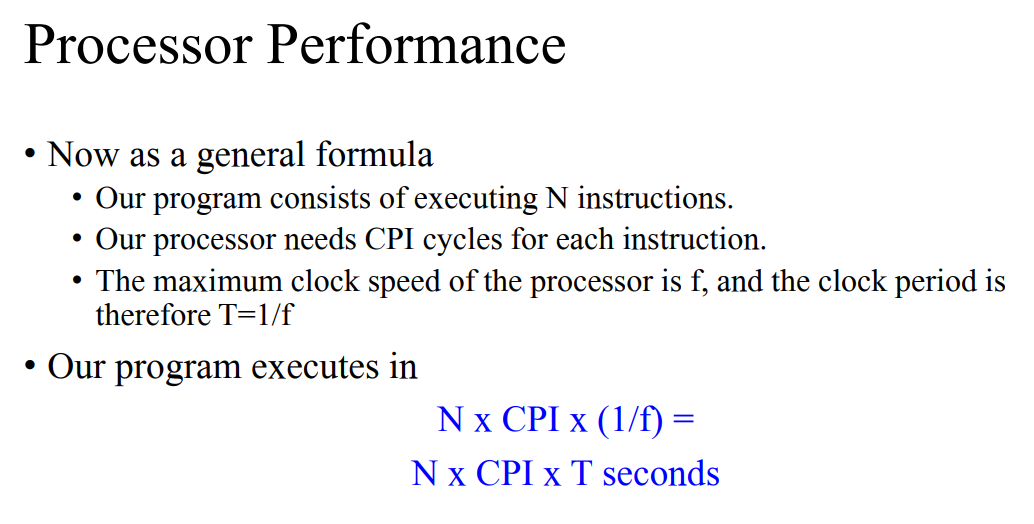

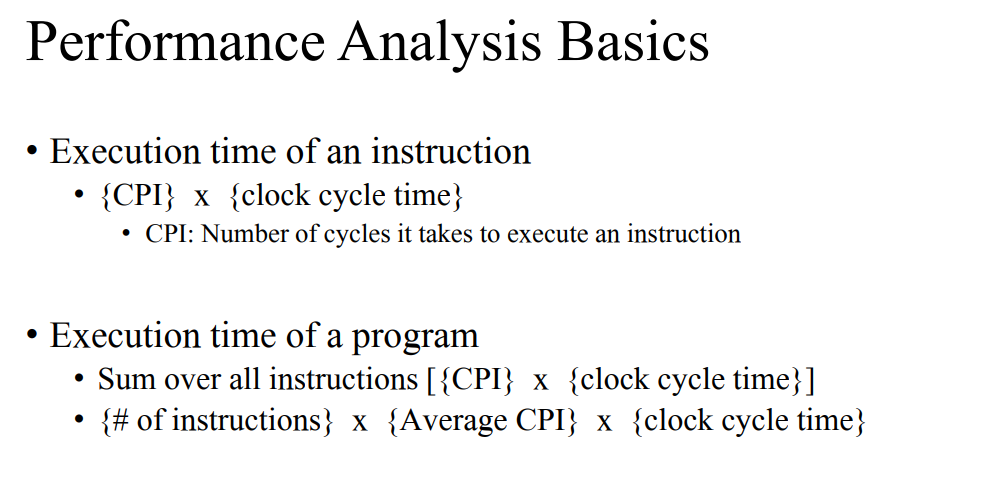

Processor Performance

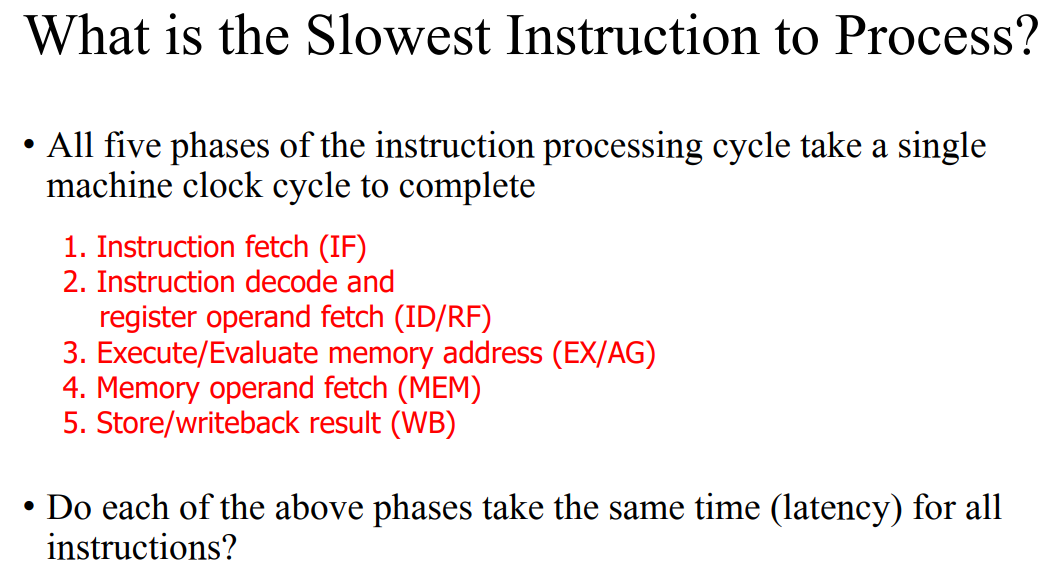

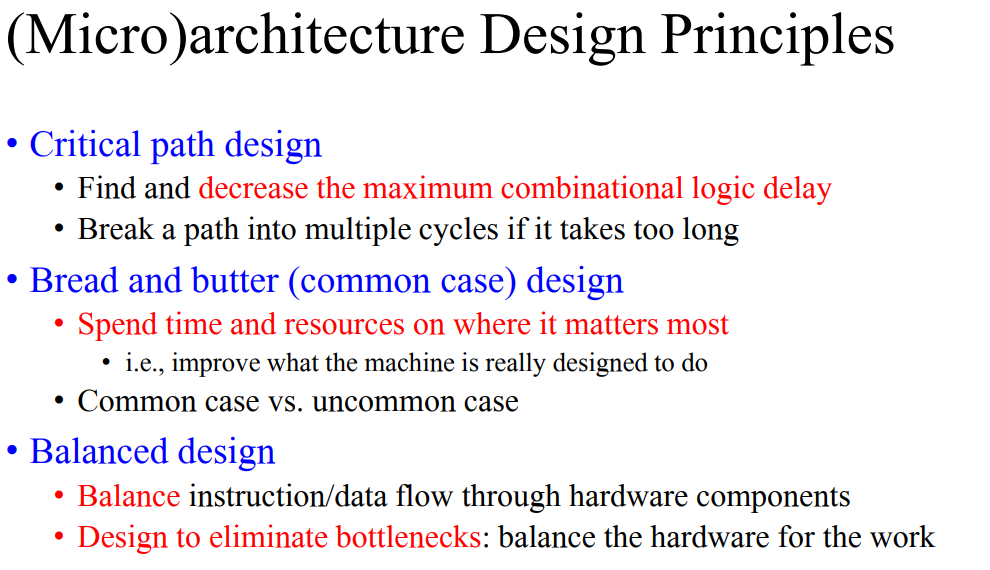

critical path는 가장 오랜 시간이 걸리는 경로를 의미한다.

- Single cycle에서는 위의 다섯가지를 모두 한 사이클에서 동작하게끔한다.

- 효율적인 메모리의 활용을 위해 위의 다섯가지 동작이 함께 동작해야한다. 이를 고려하지 않으면 앞 단계를 하고 있을 때는 다음 단계들이 모두 동작하지 않는다.

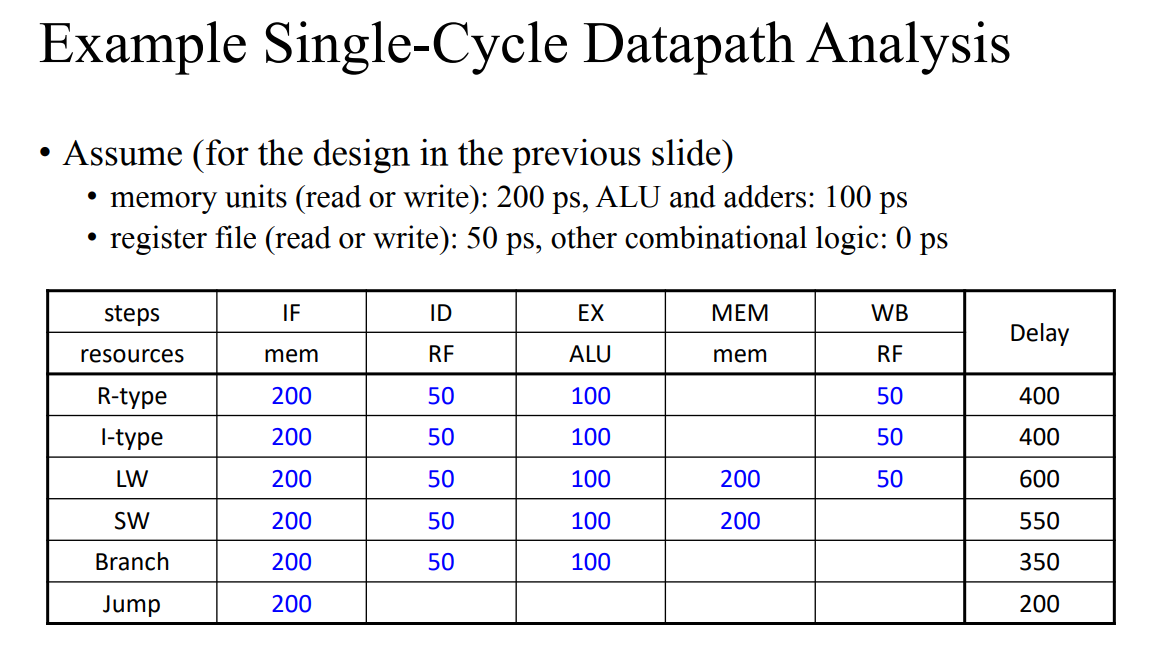

Example Single Cycle datapath analysis

회로 상에서의 datapath analysis

LW

- LW와 SW는 데이터 메모리를 사용하기 때문에 시간이 더 오래걸린다.

- D램에 접근하는 경우에는 훨씬 오랜 시간이 걸린다.

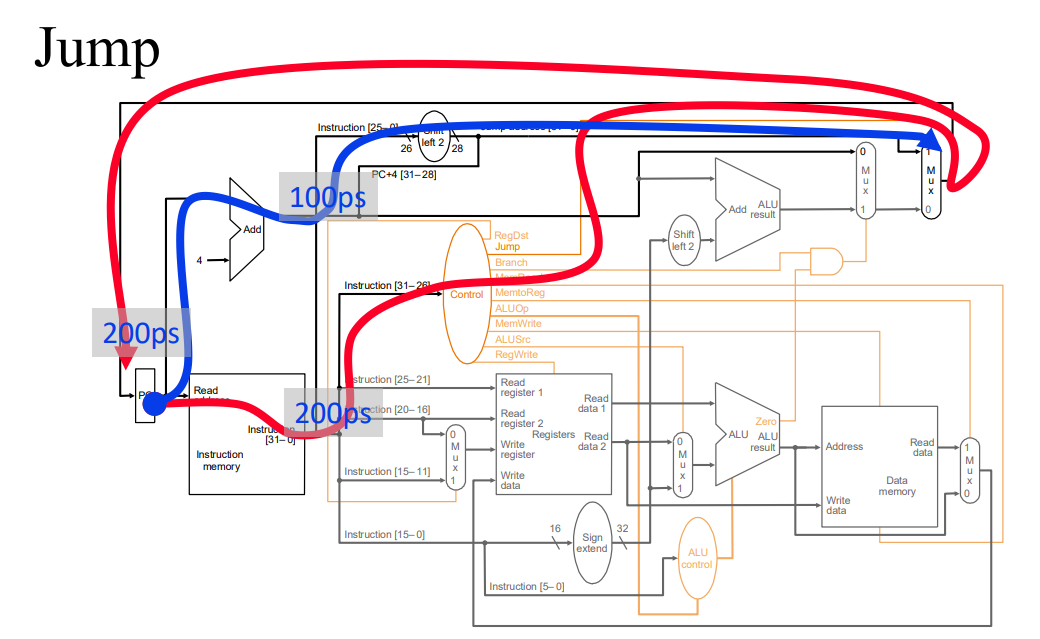

Jump

점프는 매우 빠르게 동작하는 것을 확인할 수 있다.

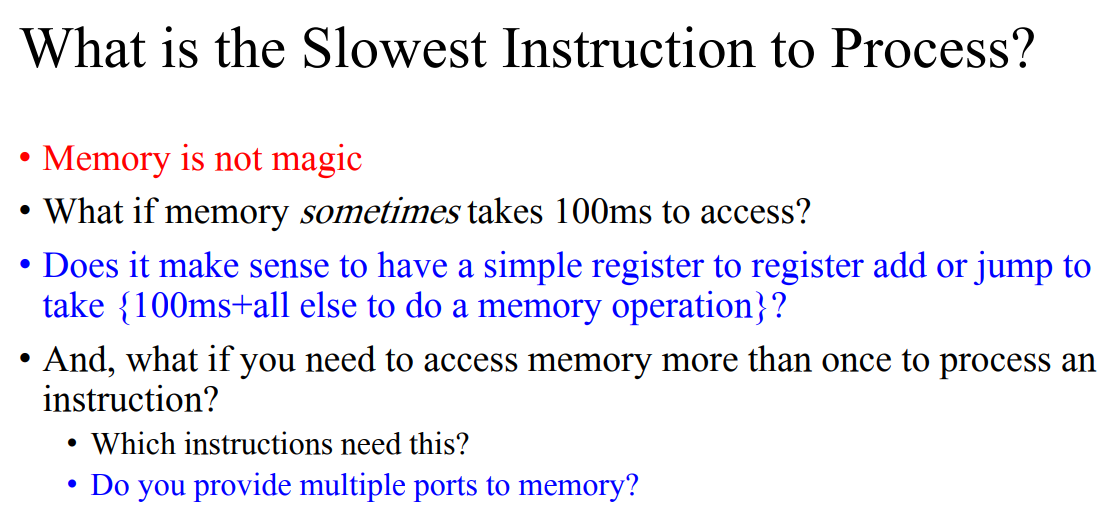

- 극단적인 경우에 메모리에 접근하는 경우에는 레지스터에서 데이터를 읽는 경우보다 훨씬 더 오래걸린다.

주의 사항

- 병목현상을 줄여주는 것이 중요하다.

파이프라인

위의 문제를 해결하기 위해 파이프라인이 필요하다.

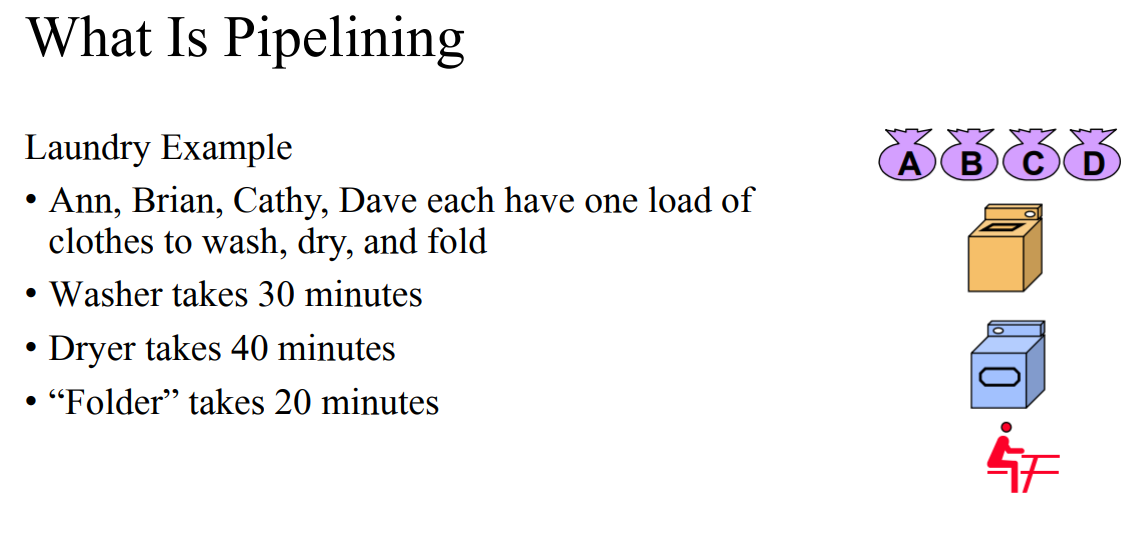

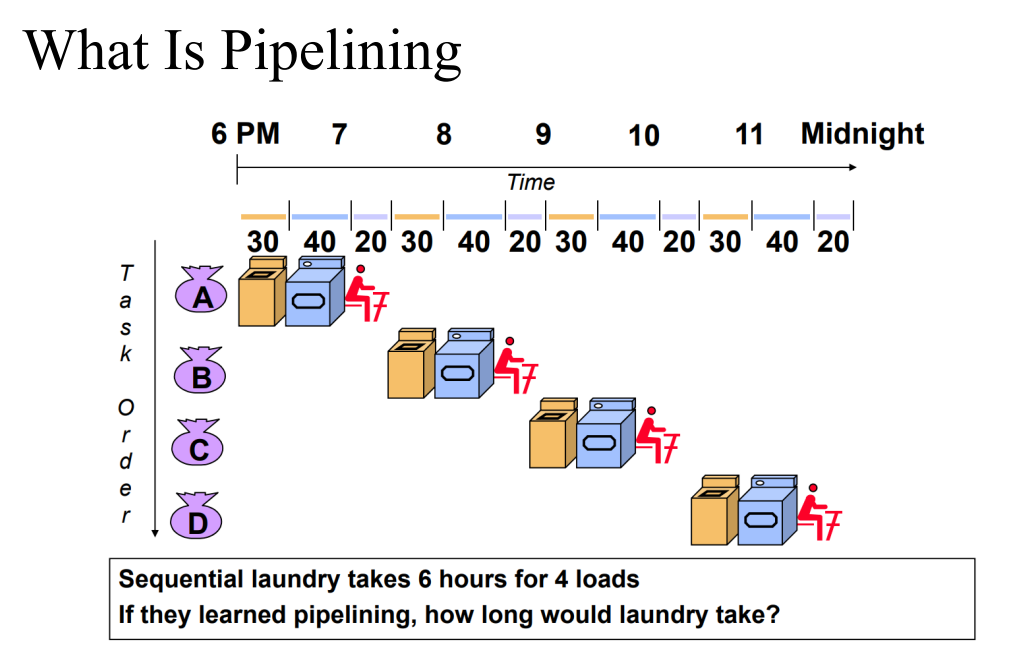

세탁기 예제)

- 모든 작업이 끝났을 때 세탁을 하면 너무 오랜 시간이 걸린다.

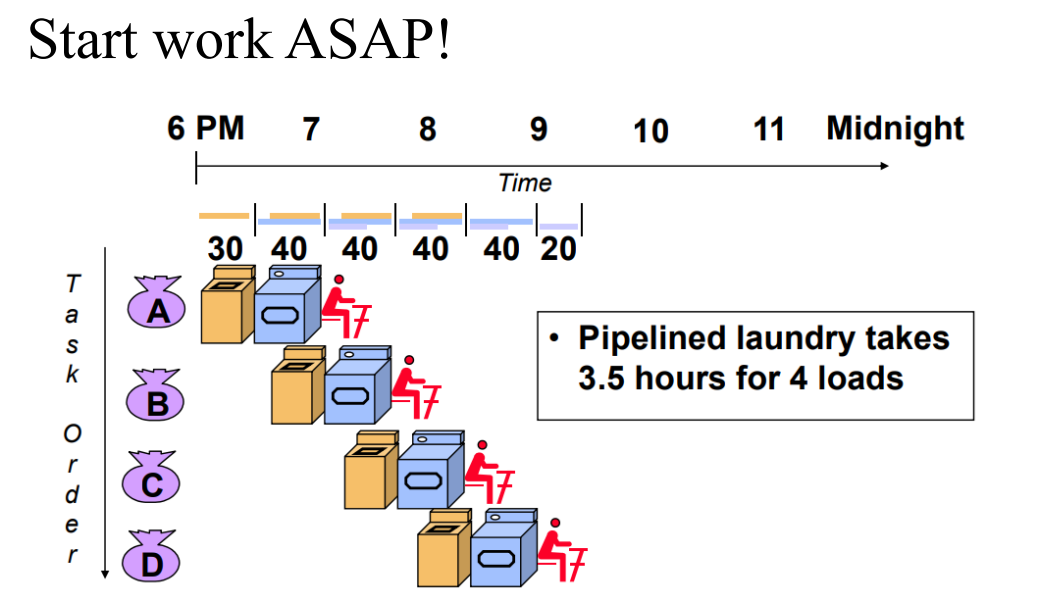

- 파이프라인을 사용하면 다음과 같이 된다.

- 위와 같이 각 활동이 끝나면 다음 사람이 사용하도록 하면 더 많은 시간을 절약할 수 있다.

- 위의 예제에서 특징은 건조기와 세탁기를 돌리는 시간의 차이 때문에 이전 사람의 건조기가 끝나자마자 바로 건조기를 돌리지 않고, 가장 오래 걸리는 동작에 대한 활동을 기준으로 최적화하는 것이 더 좋다.

- ex) 건조기 30분, 세탁기 40분이 걸린다면 이전 사람의 건조기가 끝나자마자 이를 돌리면 건조기가 끝나고도 이전 사람의 세탁기를 기다려야하기에 이를 고려해 건조기를 돌린다.

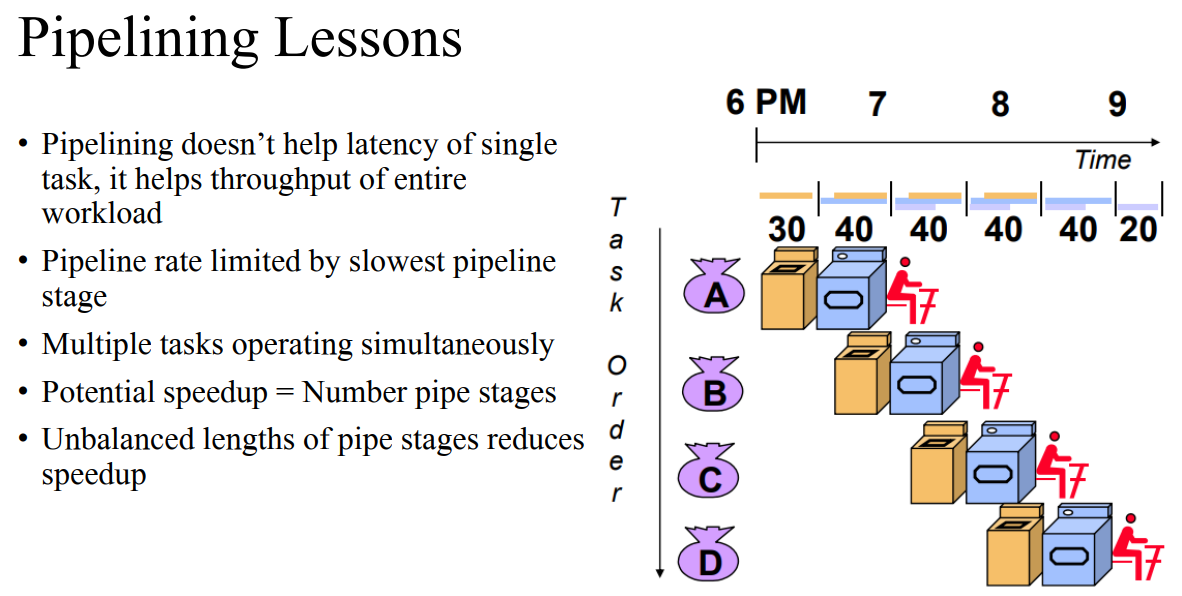

- single task의 latency는 똑같지만 여러 명이 일할 때 효율적이다는 것을 확인할 수 있다.

- 단계가 많을수록 speed up이 될 수 있는 여지가 많아진다.

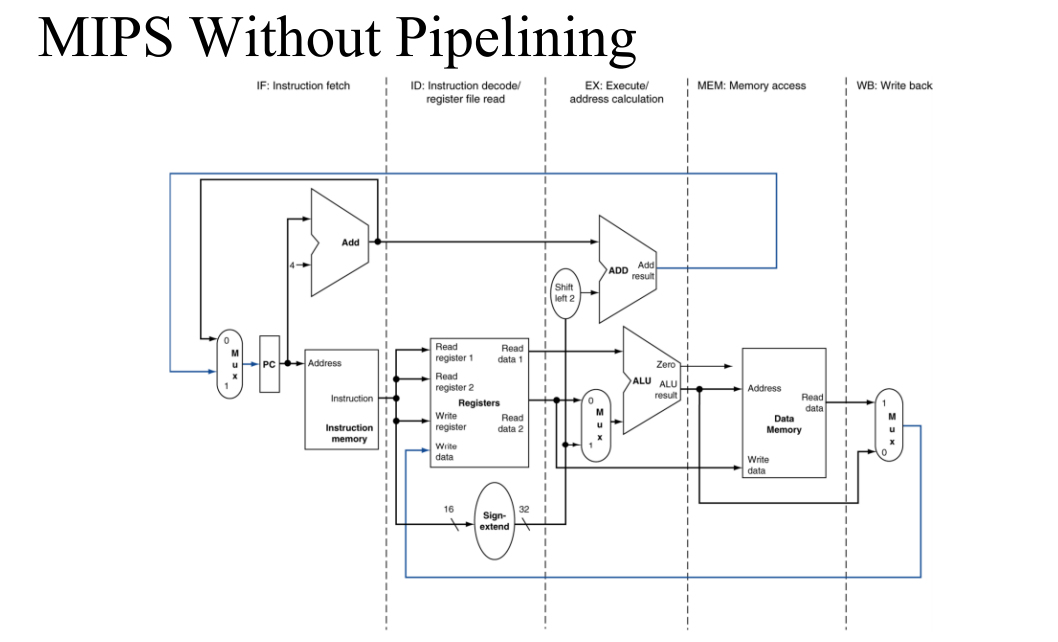

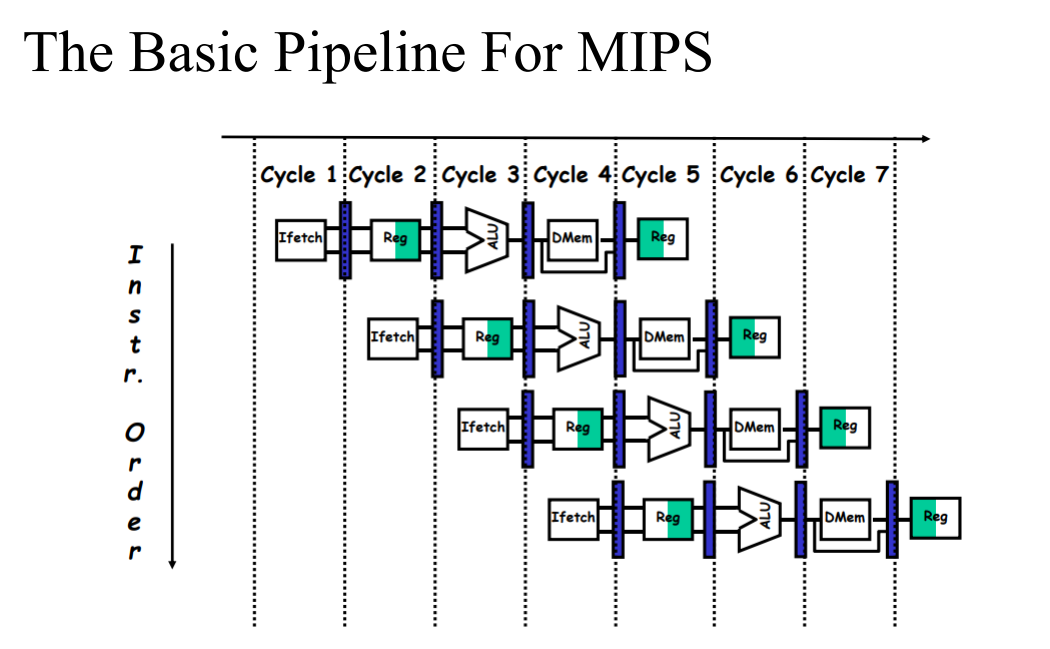

파이프라인이 없는 경우의 MIPS

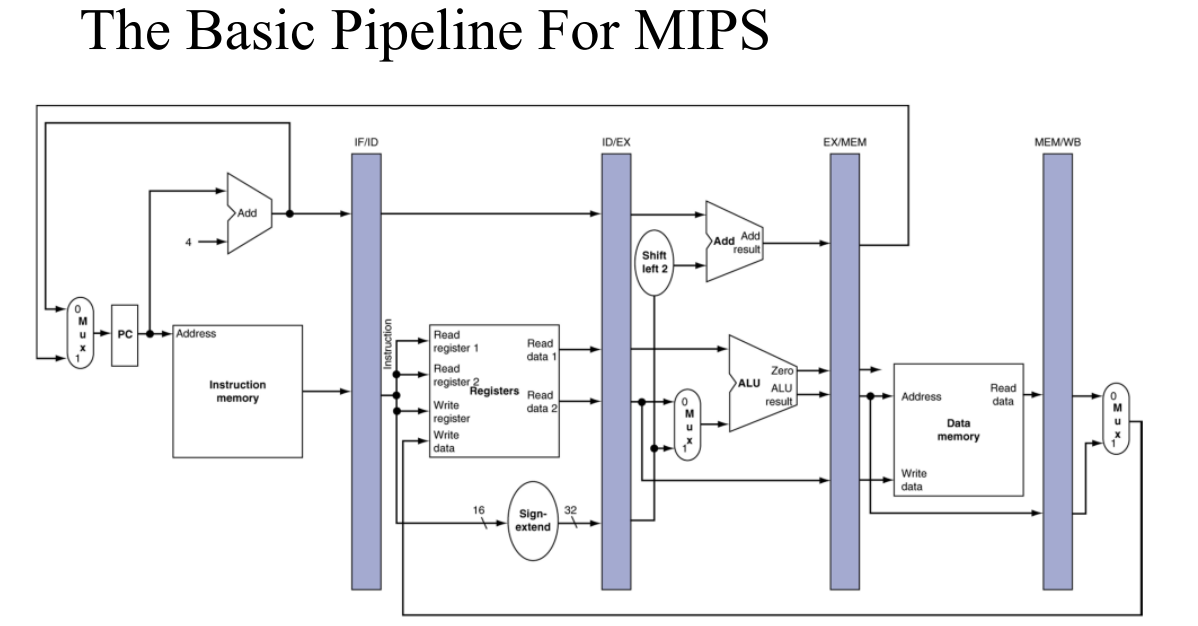

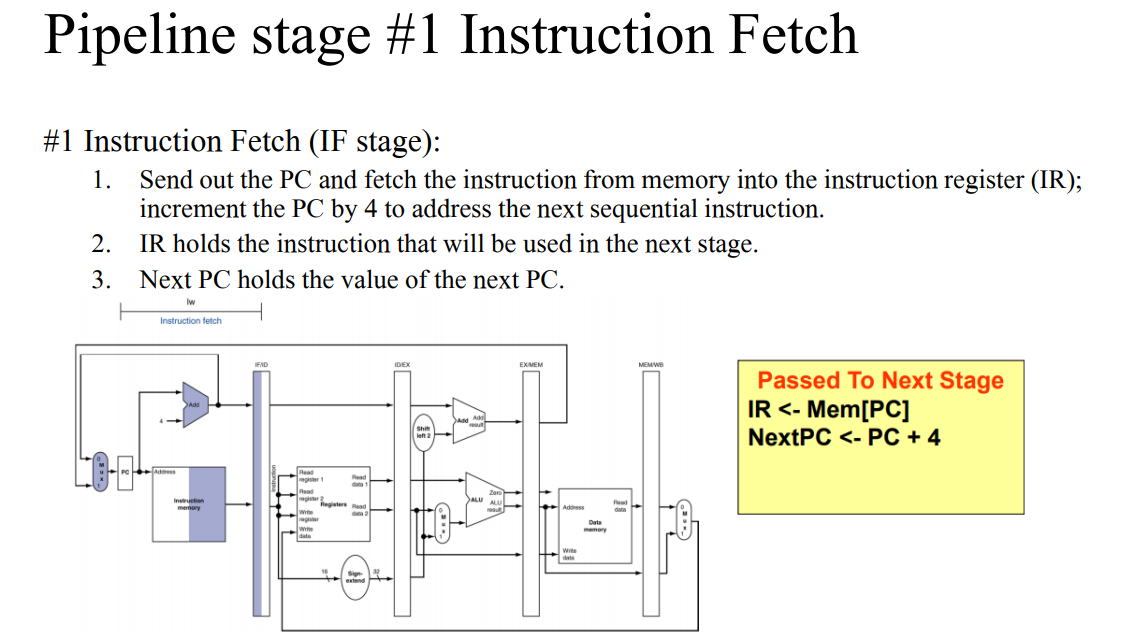

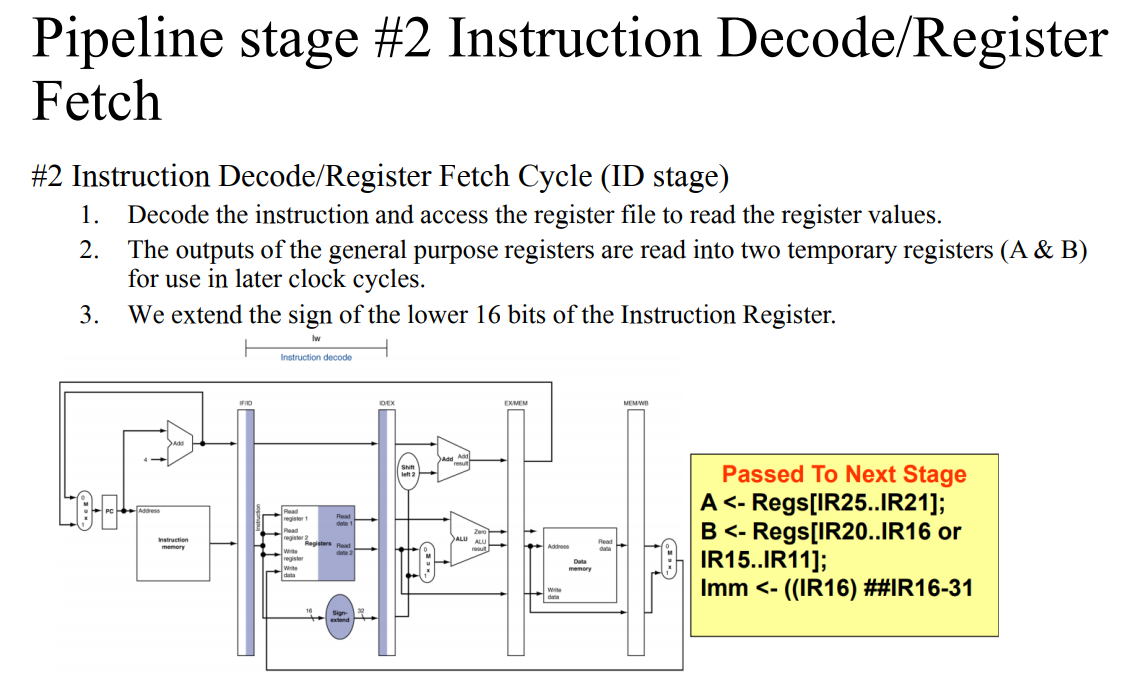

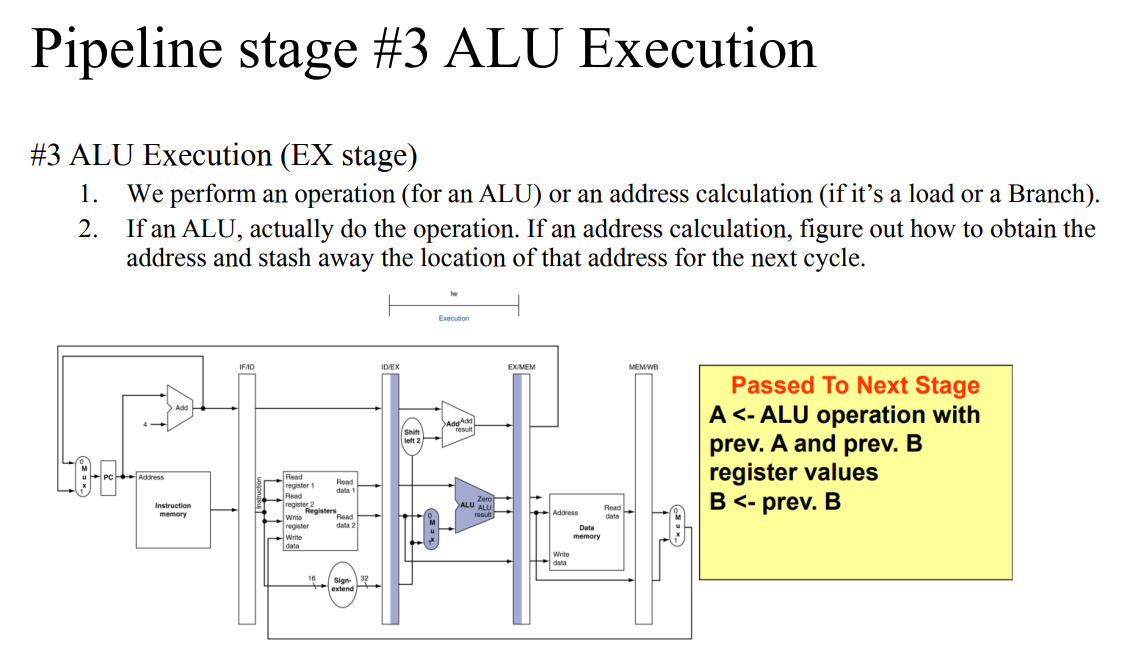

- MIPS에 파이프라인을 구현할 때는 크게 다섯단계로 나눠서 진행한다.

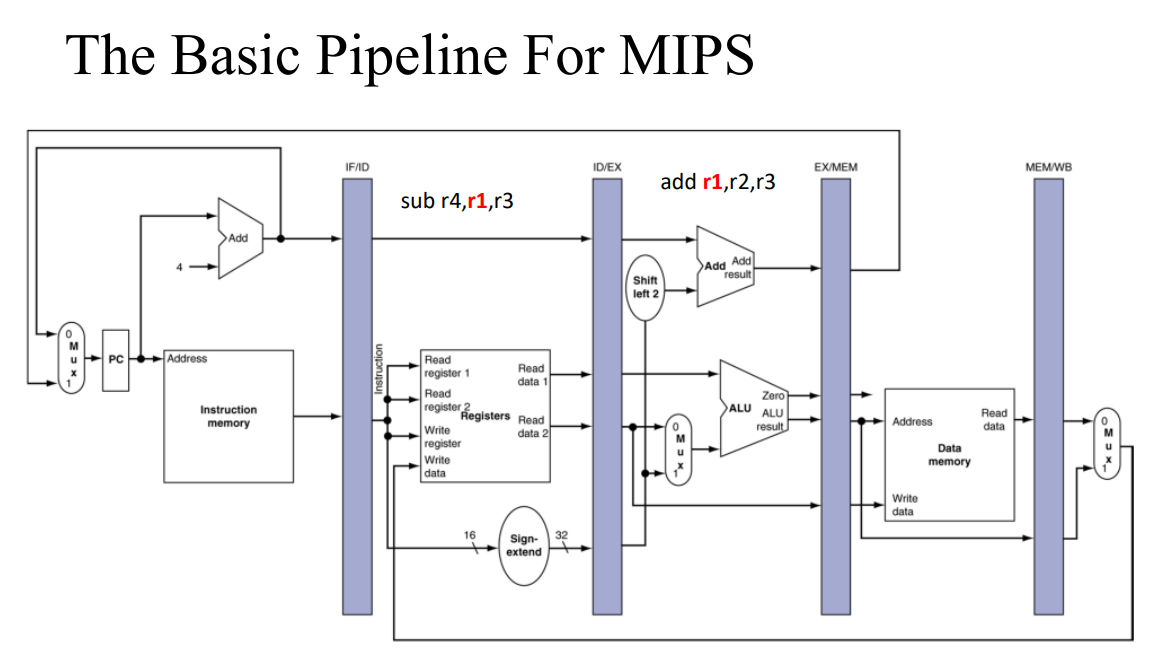

- 각 스테이지 사이에 레지스터를 추가해줘서 총 네개의 레지스터가 추가된다.

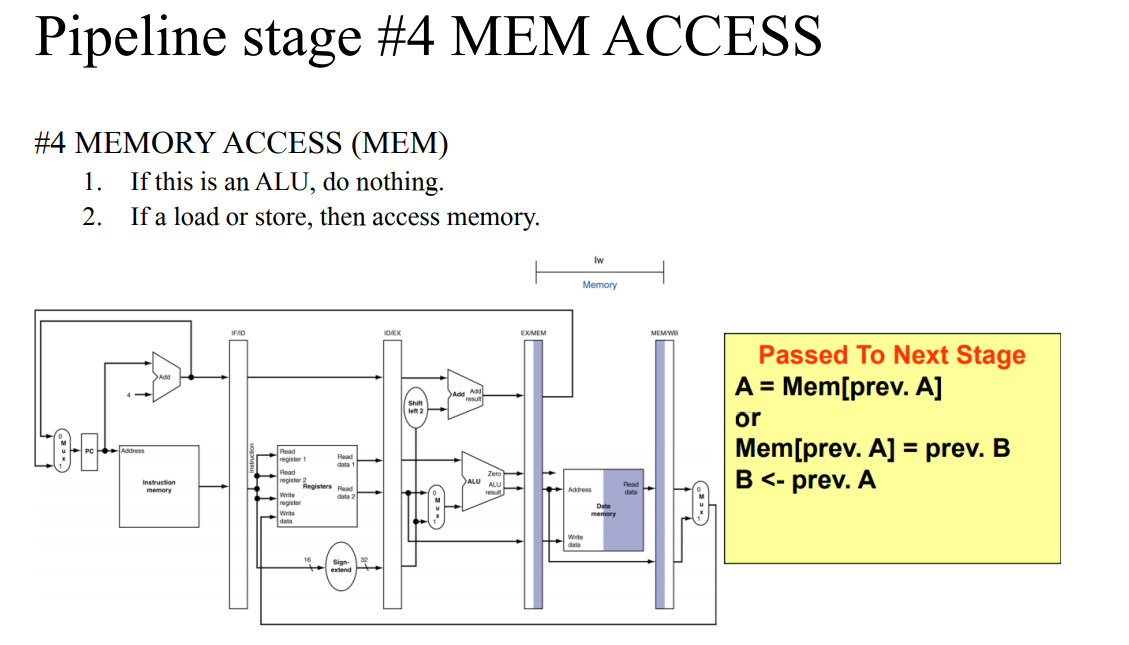

파이프라인 단계

- 3단계는 load word일 때 어떤 동작을 하는 지의 관점으로 고려할 수 있다.

- 4단계는 메모리와 관련된 동작을 하는 것으로 고려할 수 있다.

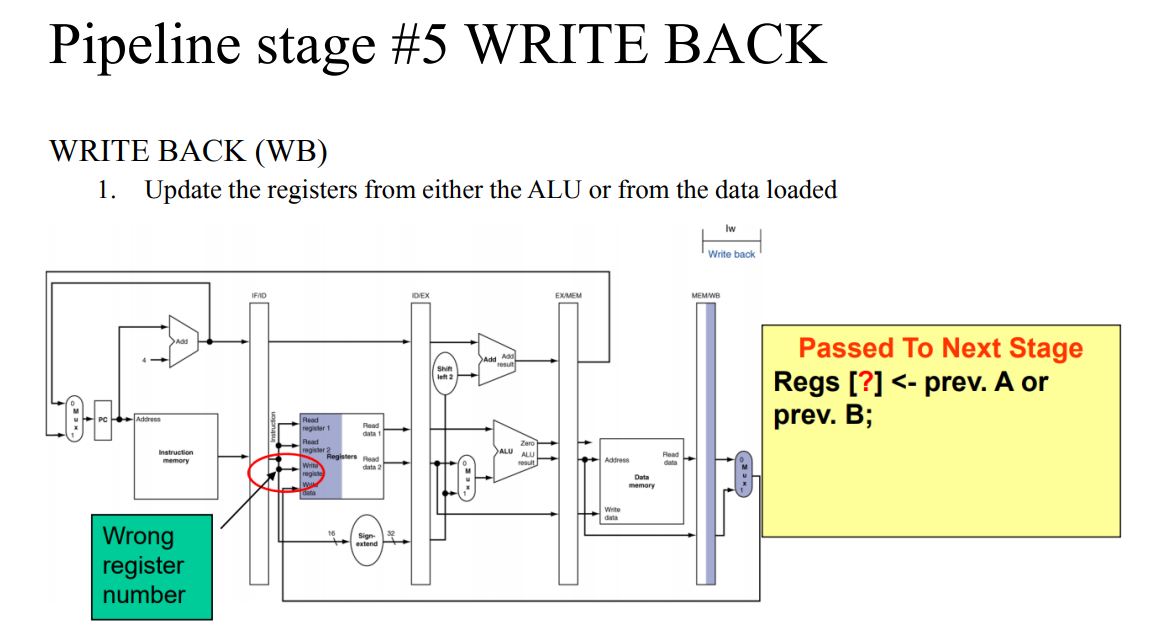

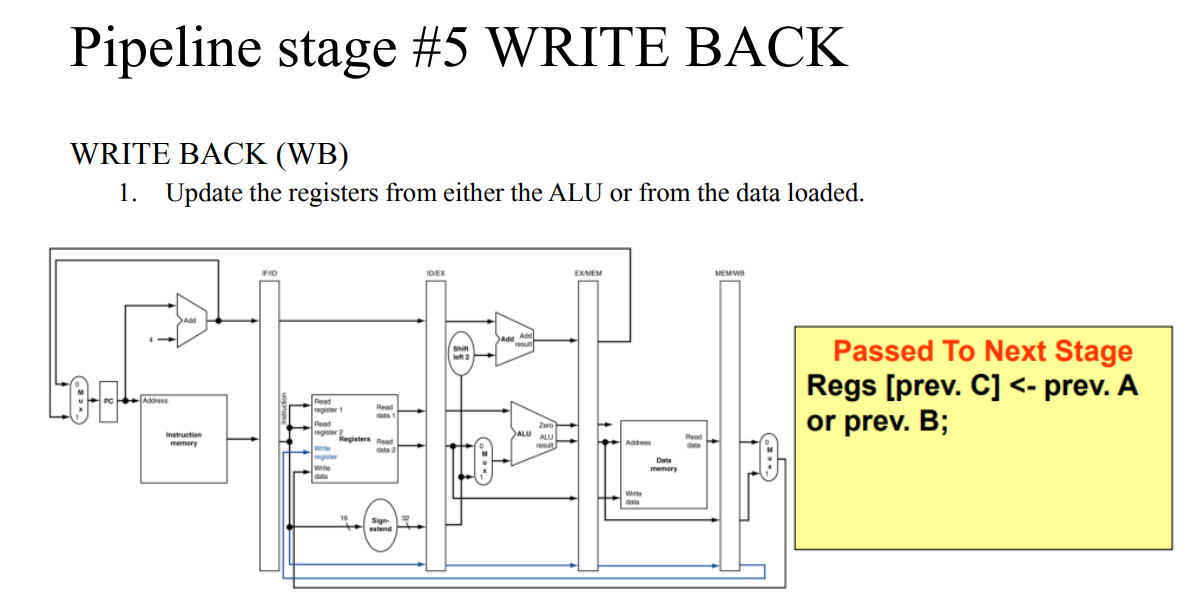

- Single Cycle을 할 경우에는 문제가 발생하지 않았지만 파이프라인을 하면서 위와 같은 문제점이 발생할 수 있다.

- Write data가 입력되는 것과 데이터를 불러오는 것과의 간격 때문에 문제가 발생할 수 있다. 이를 해결하기 위해 아래와 같이 Write register에 들어온 값도 넘겨준다.

- 각 사이클별로 패치를? 진행한다.

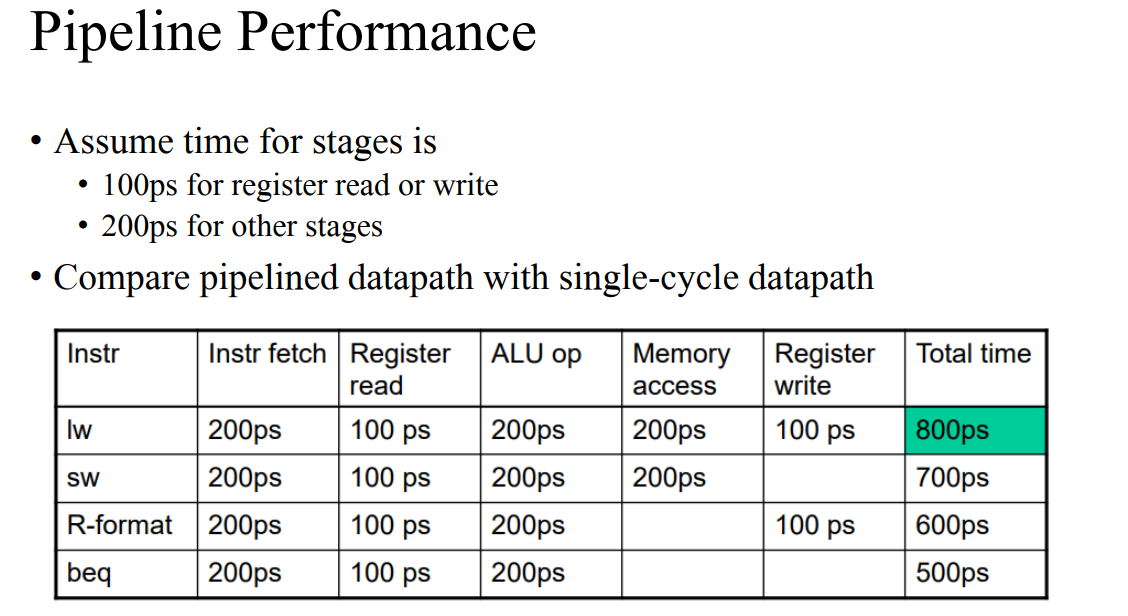

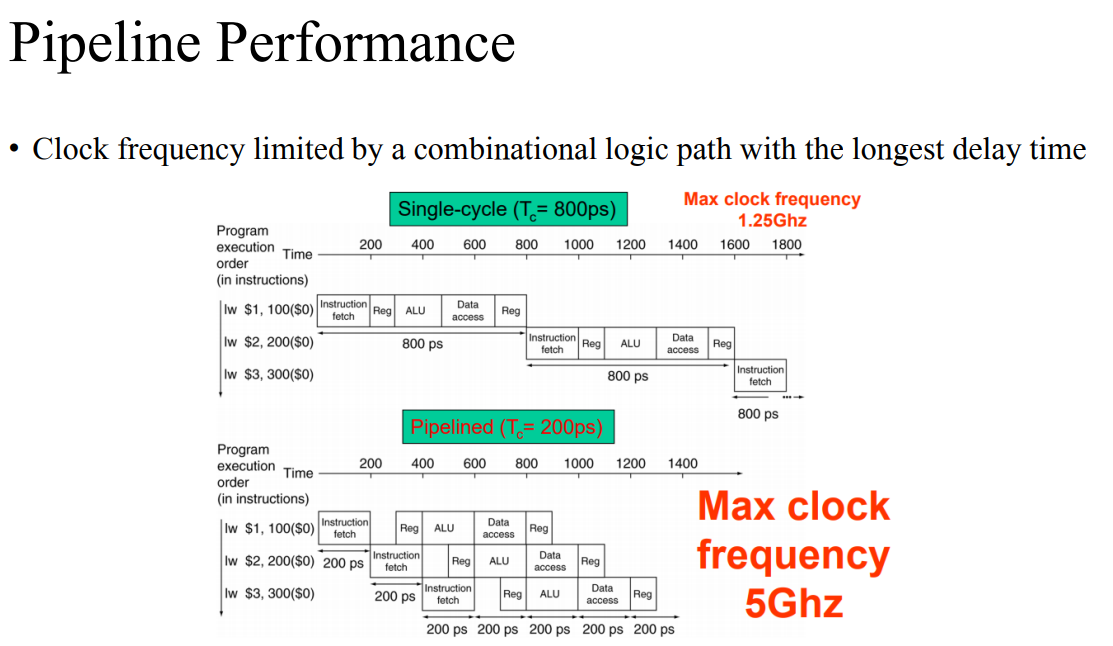

- 레지스터에서 데이터를 read 혹은 write할 때의 lw가 가장 오래 걸린다. single cycle의 경우에는 800ps에 하나씩 사이클이 돈다.

- 파이프라인은 각 단계에서 소모되는 시간 중 가장 긴 200ps를 기준으로 맞추면 된다.

- 이에 따라 pipeline은 속도가 4배 빨라진다.

파이프라인에서 주요한 이슈

- 밸런스 있게 단계를 쪼갠다면 속도의 향상을 이룰 수 있다.

- defendency 때문에 생각한 만큼 파이프라인이 동작하지 않을 수 있다. ex) 만약에 모든 명령이 하나의 리소스에 접근한다면 동작하지 못할 수 있고, 브랜치 명령에서 pc값이 바뀔 때 어떤 것을 패치해야하는지 모르는데 패치해야하는 이슈, 데이터 로드 간격 등에 따른 에러가 발생할 수 있다. 또한 ALU 연산이 프로세서에 따라 다르기 때문에 파이프라인이 망가질 수 있다. 이러한 경우들에 대해 파이프라인의 instruction 패치를 기다리는 등의 stall과 같은 동작을 한다.

- 하지만 stall은 최소화하는 것이 성능을 높일 수 있다.

파이프라인 Hazards

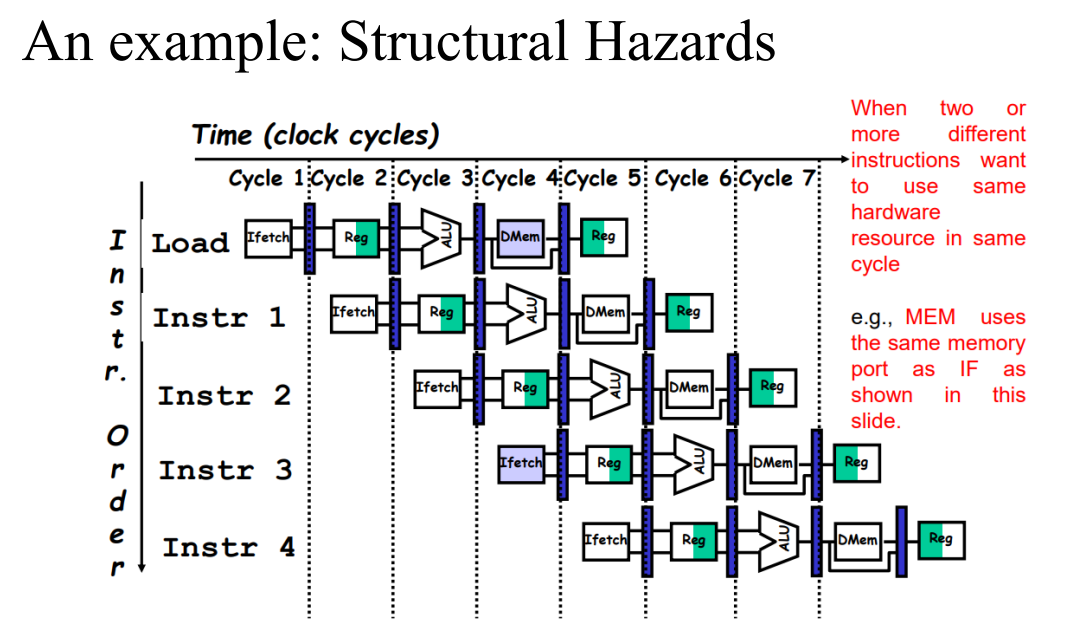

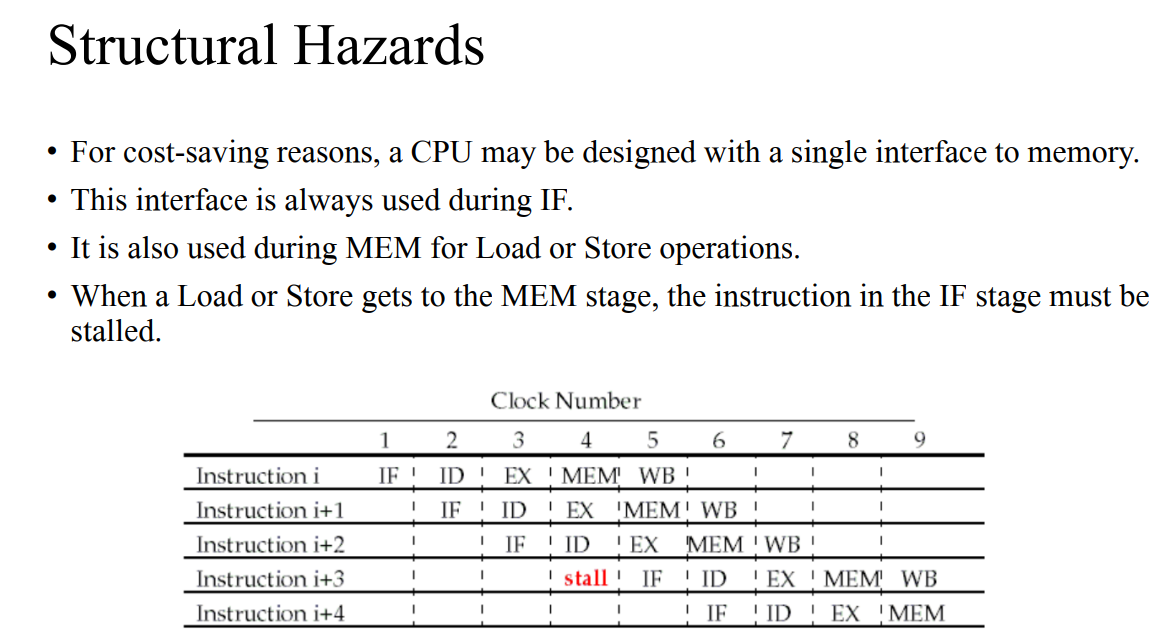

- Structural hazards: 여러 명령어가 동일한 리소스를 사용하려고 할 때

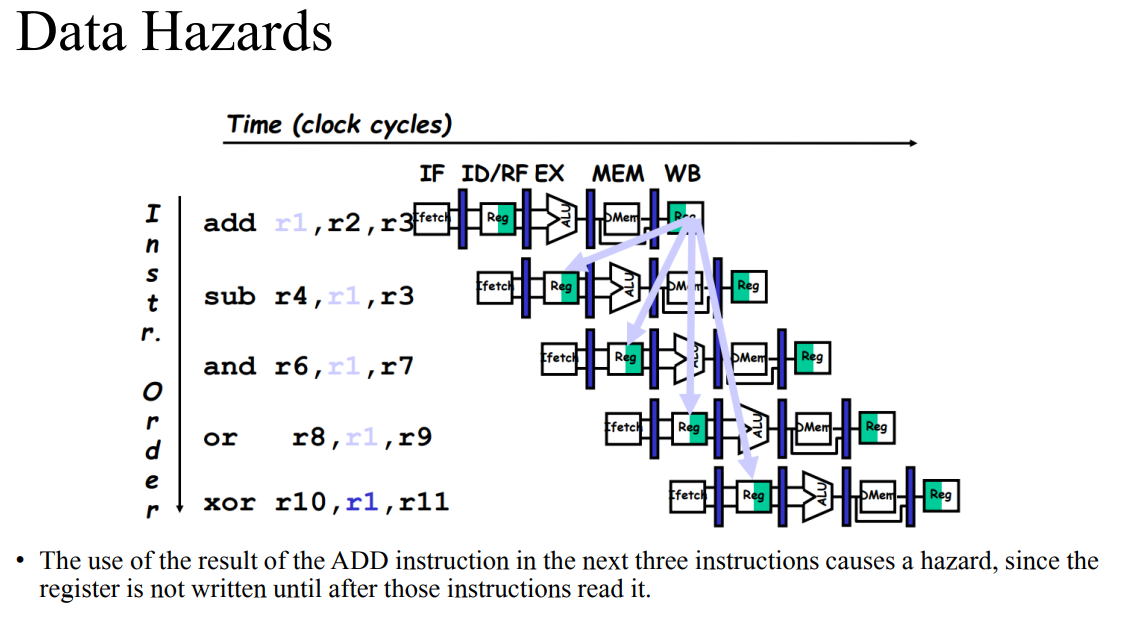

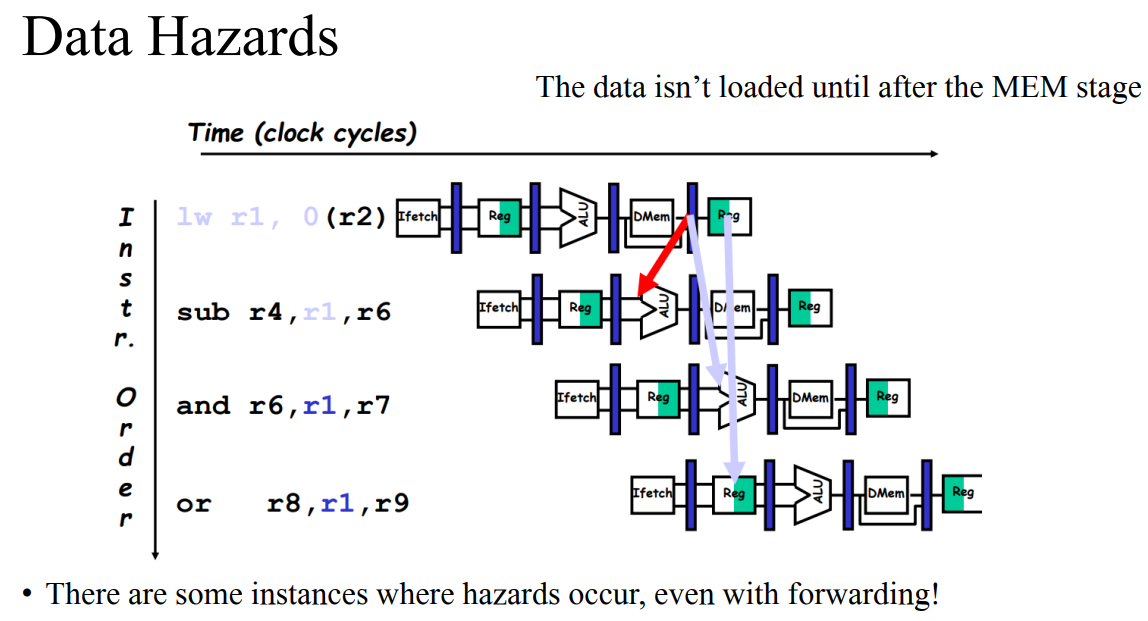

- Data hazards: 잘못된 데이터를 가지고 처리하려 할 때

- Control hazards: 브랜치나 명령어가 PC값을 바꿀 경우

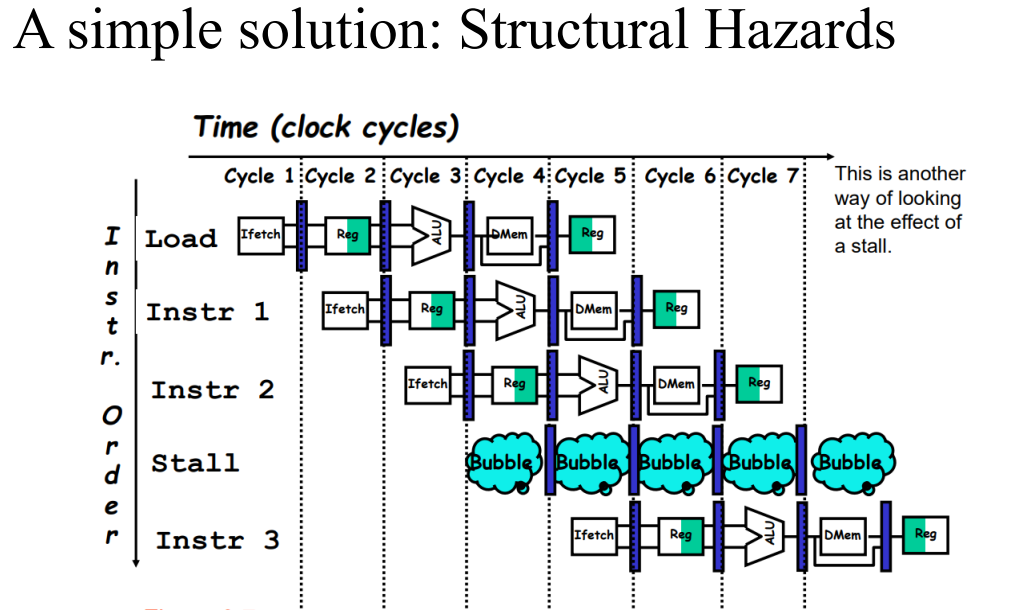

해결 방법

- stall을 진행한다. 하지만 이는 파이프라인을 멈추는 것이기에 간단하지만 성능은 떨어지게 되므로 이를 최소화하는 것이 중요하다.

(1) Structural Hazards

- 여러 명령어들이 동일한 메모리 주소를 접근하려고 한다.

해결 방법

- bubble을 넣어서 stall한다.

- 각 스테이지에서 정해진 리소스만 사용하도록 하고 한 사이클에 해당하는 리소스만 사용하게 하면 Structural Hazards를 줄일 수 있다.

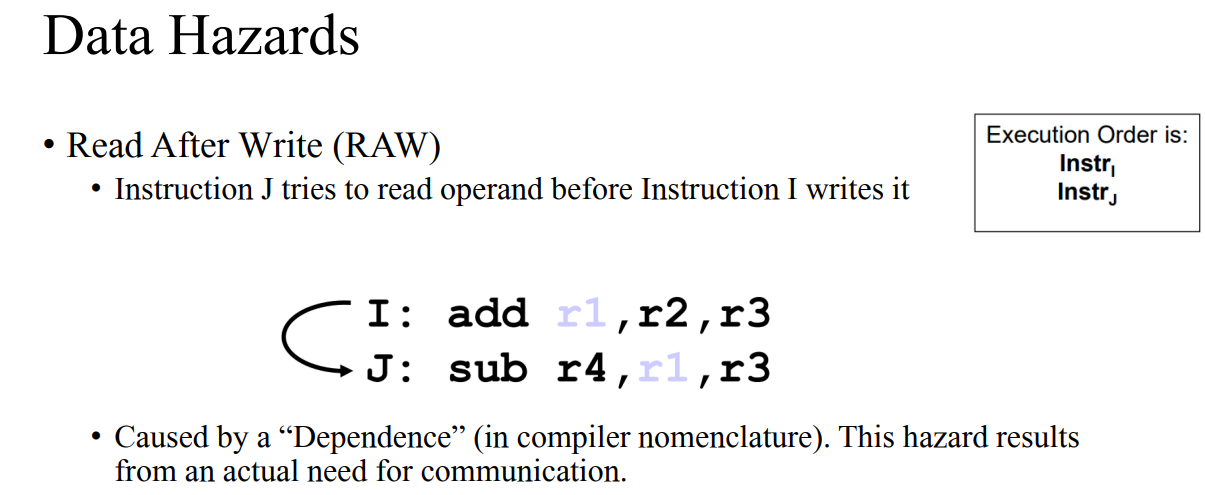

(2) Data dependence

- flow dependence의 경우 시멘틱하게 맞는지 체크하는 과정이 필요하다.

- MIPS가 아닌 곳에서는 output anti?를 신경써야할 수 있다.

종류

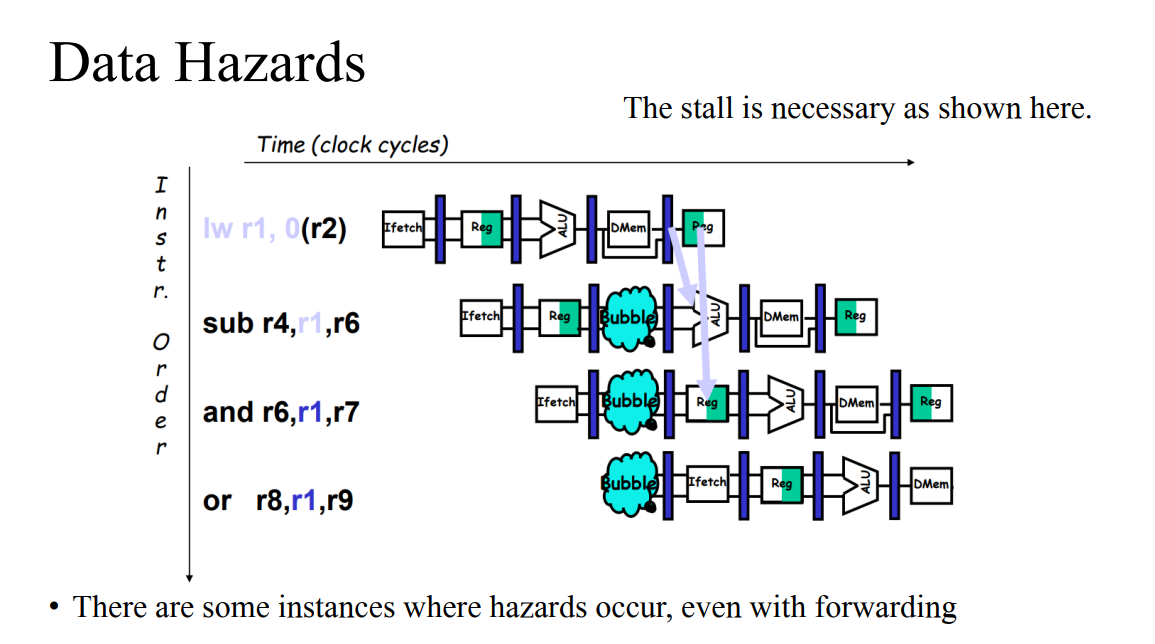

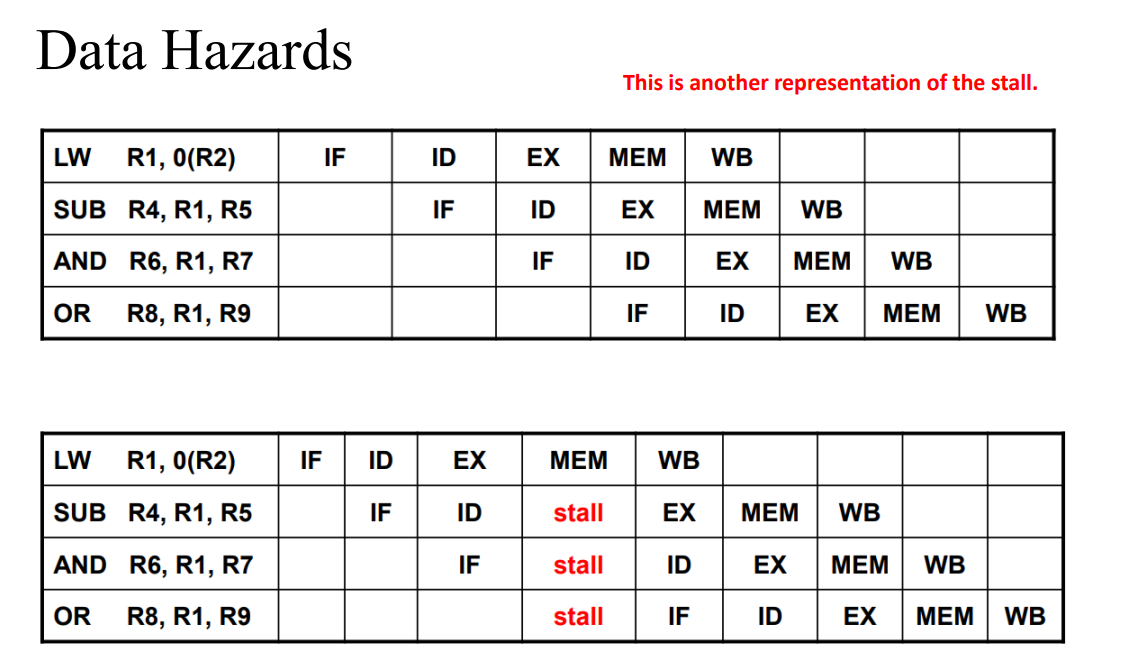

- 파이프라인을 통해 위의 내용을 구현하고자 한다면 계산을 하는 중에 r1값을 read하기에 문제가 발생할 수 있다. 즉, 업데이트하기 전에 데이터를 read하기 때문에 문제가 발생한다.

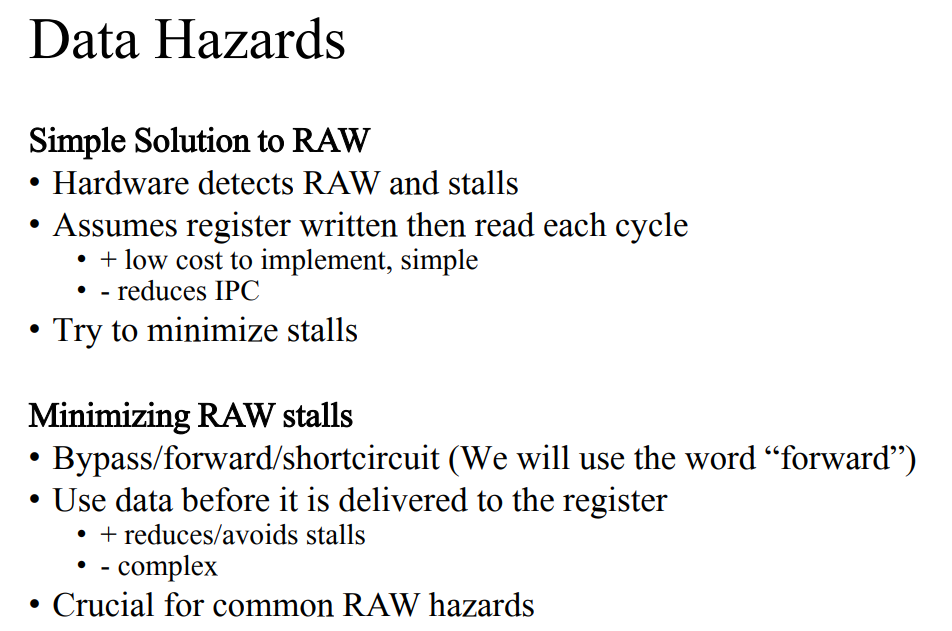

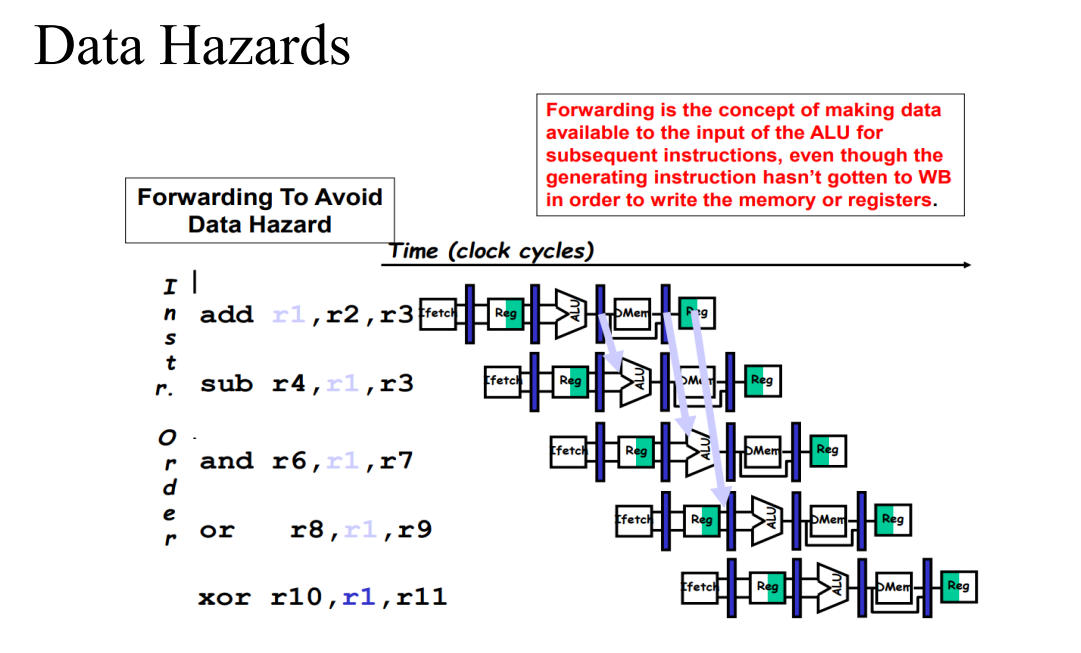

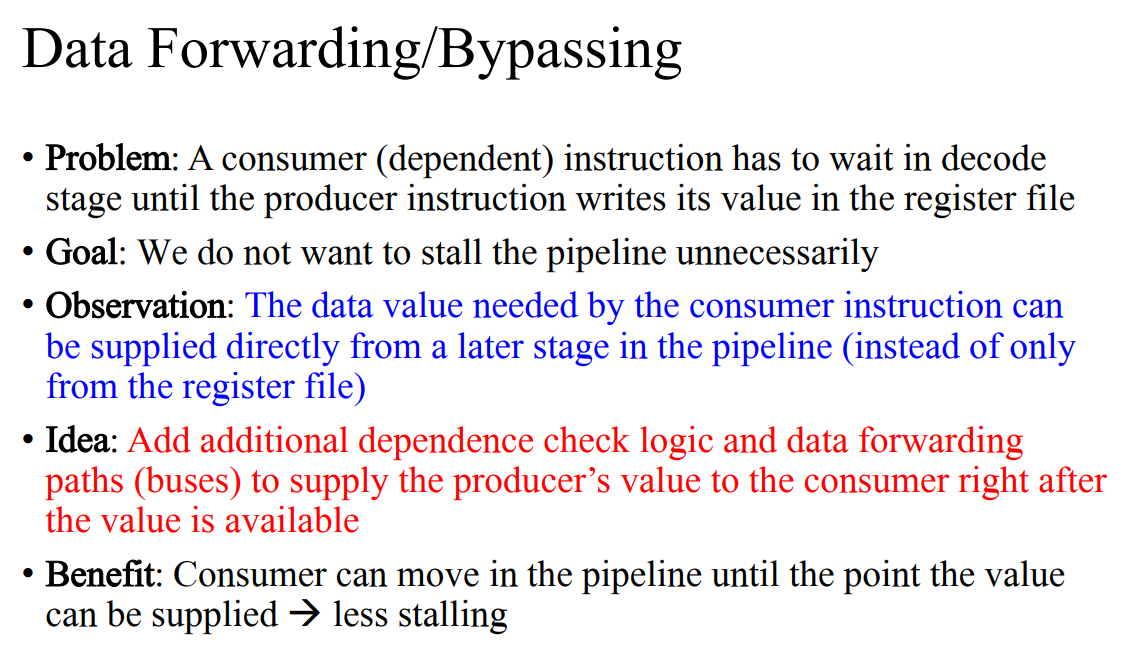

- 해결방법

- 가장 간단한 해결 방법은 stall하는 것이다. 하지만 연달아 연산을 하는 경우에는 오랫동안 stall을 해야하기에 구현은 쉽지만 성능은 줄어든다. 이에 따라 shortcircuit(forward)를 만들어 write back해서 이를 레지스터에 저장하기 전에 값을 넘겨준다.

기존

- 계속 stall 해야하기에 오래 기다려야한다.

forwarding

연산의 결과값을 미리 전달해 다음 명령어에서 데이터를 이용할 수 있도록 도와줄 수 있다. 이에 따라 다음 사이클에 바로 활용할 수 있다.

위와 같이 한다면 문제가 발생하기에 stall을 해야한다.

'강의 내용 정리 > 컴퓨터구조' 카테고리의 다른 글

| 컴퓨터 구조(8), Branch Prediction (0) | 2022.06.08 |

|---|---|

| 컴퓨터 구조 (7), Pipelining (0) | 2022.05.23 |

| 컴퓨터 구조 (5), Instruction Set Architecture 02 (0) | 2022.04.21 |

| 컴퓨터 구조 (3), Sequential Logic Circuits and Design (0) | 2022.03.22 |

| 컴퓨터 구조 (2) Combinational Logical Circuits and Design (0) | 2022.03.15 |