2022. 3. 22. 16:10ㆍ강의 내용 정리/컴퓨터구조

Sequential Logic Circuits and Design, 순차회로

1. 순차회로란?

과거의 input value를 메모리 형태로 가지고 있어서 해당 값과 현재 input value로 output을 결정하는 회로

1) Cross-Coupled Inverter

- 이는 Q를 컨트롤해주는 메카니즘이 필요하다.

2) Storage Elements

(1) Latches and Flip-Flops

- 매우 빠르고 병렬도 접근 가능하다.

- 1비트를 저장하기 위해 10개의 트렌지스터가 필요하기에 비싸다.

(2) Static Ram(SRAM)

- 래치와 플립플롭보단 느리지만 다른 것들과 비교했을 때 상대적으로 빠르다.

- 1비트를 저장하기 위해 6개 이상의 트렌지스터가 필요하기에 상대적으로 비싸다.

(3) Dynamic Ram(DRAM)

- 하드디스크보단 빠르지만 비교적 느리고, 리프레쉬가 필요하다.

- 1비트를 저장하기 위해 1개의 트렌지스터와 1개의 capacitor가 필요하기에 상대적으로 저렴하다.

(4) Other storage technology(flash memory, hard disk, tape)

- 시간이 엄청 오래걸리지만 데이터가 날라가지 않는다.

- 가격이 매우 저렴하다.

3) Latch

(1) R-S Latch (Cross-coupled NAND gates)

- S가 1이고 R이 1인 경우 이전 상태를 그대로 이어감 -> stable한 상황

- S가 1이고 R이 0인 경우 Q는 1이 됨

- S가 0이고 R이 1인 경우 Q는 0이 됨

- S가 0이고 R이 0인 경우에는 논리적으로 불가능함 -> 불안정한 상태가 됨 (R-S 래치의 결점)

(2) Gated D Latch

- R-S Latch를 보완하여 D의 값과 Write Enable 값을 조정하여 불안정한 상태를 없앰

- Write Enable로 모두 연결이 되어있기에 동시에 작성할 수 있음

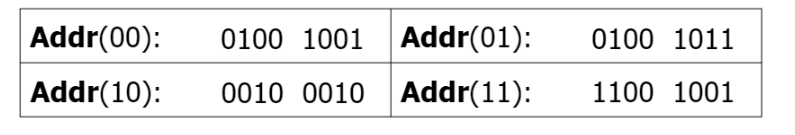

4) Memory

- Addressability: 각 주소에 저장하고자 하는 비트수의 숫자 (위에선 8 bits)

- Address space: 메모리를 저장할 수 있는 유일한 메모리 공간에 대한 set

- decoder 역할과 multiplexer 역할을 하는 게이트가 존재함

- 블럭에는 D-Latch가 들어갈 수 있음

- Addr와 WE의 AND gate 조합으로 줄을 선택하여 선택된 줄은 1, 선택이 안된 줄은 0의 값을 가짐

- 위에서 선택한 줄은 D-latch에서 Write Enable로 값이 전달되고 각 줄이 선택된다면 전달 받은 값을 D-latch로 넘겨줌

- 위의 과정을 고려했을 때 초록색의 선행된 부분은 Decoder의 역할을 하고, 주황색에 있는 부분은 MUX의 역할을 함

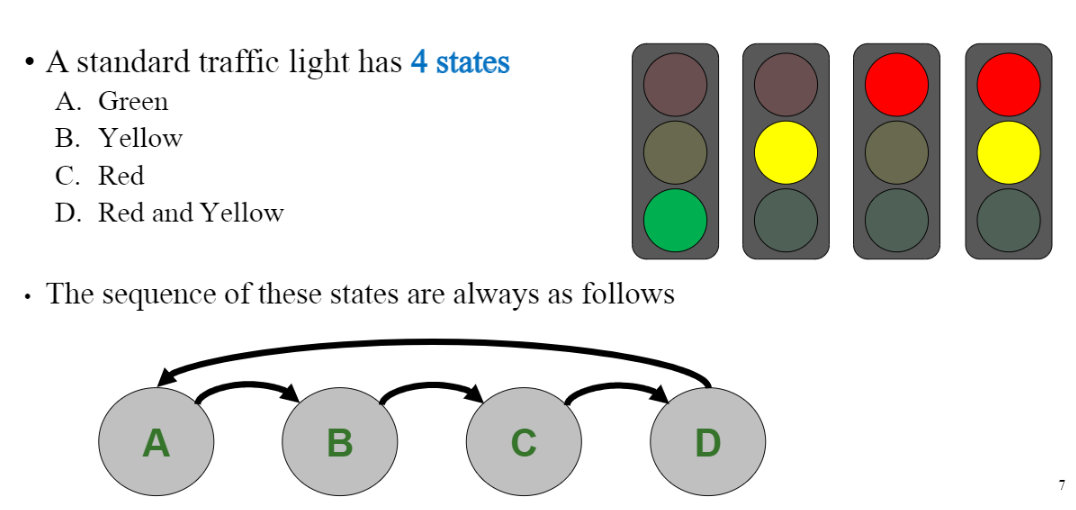

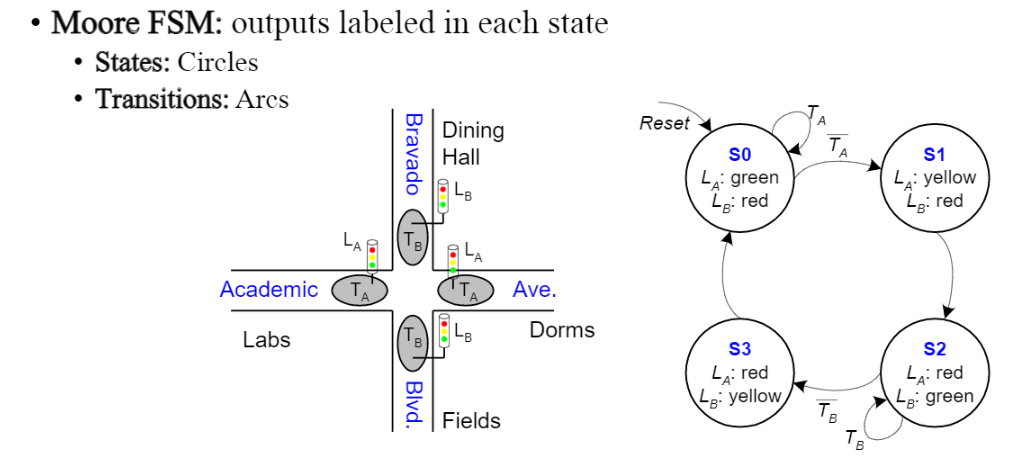

5) State Diagram

- 순차적으로 발생할 수 있는 상태들에 대해 도표로 그려 input, output, state를 나타낸 것

- 문제를 해결하기 위해선 정해진 경로를 순차적으로 거쳐야함

- 만약 다른 값이 들어오면 처음부터 시작해야함

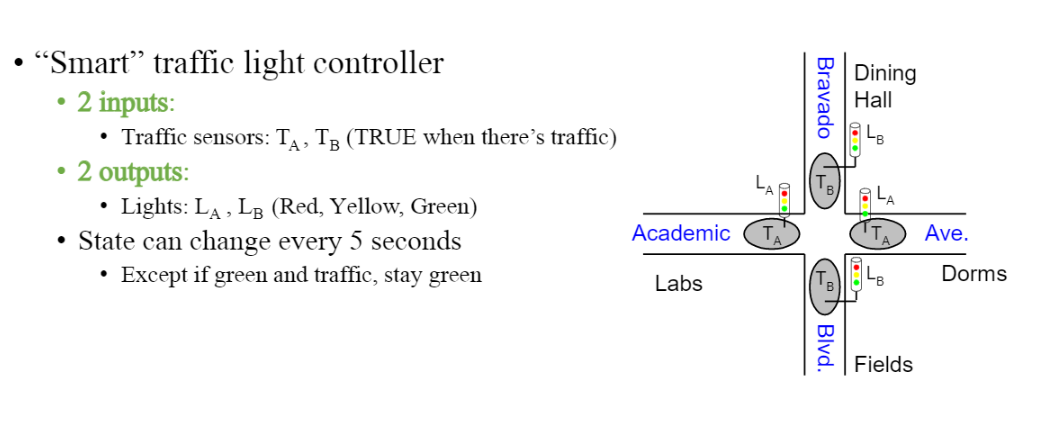

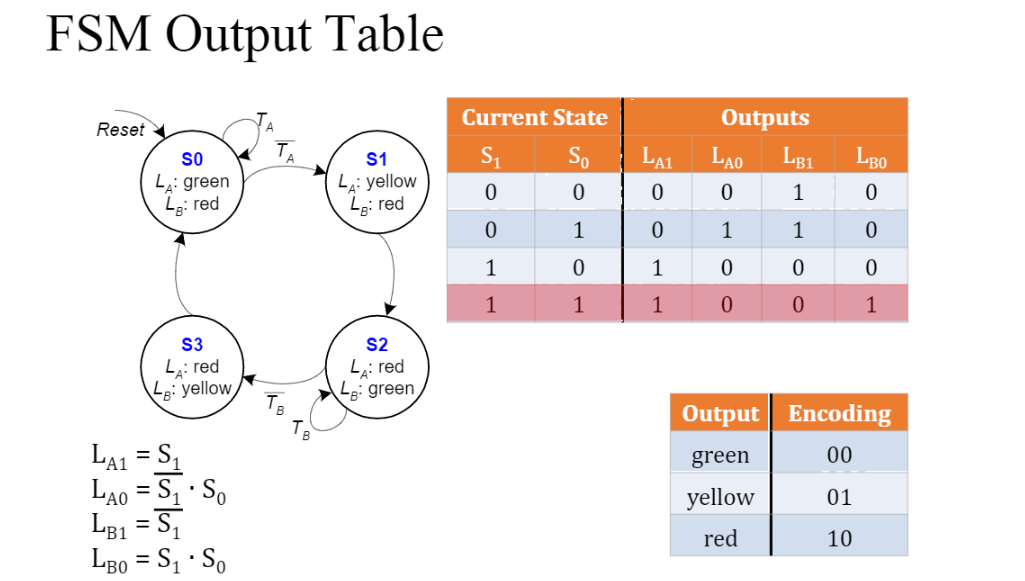

신호등 예시)

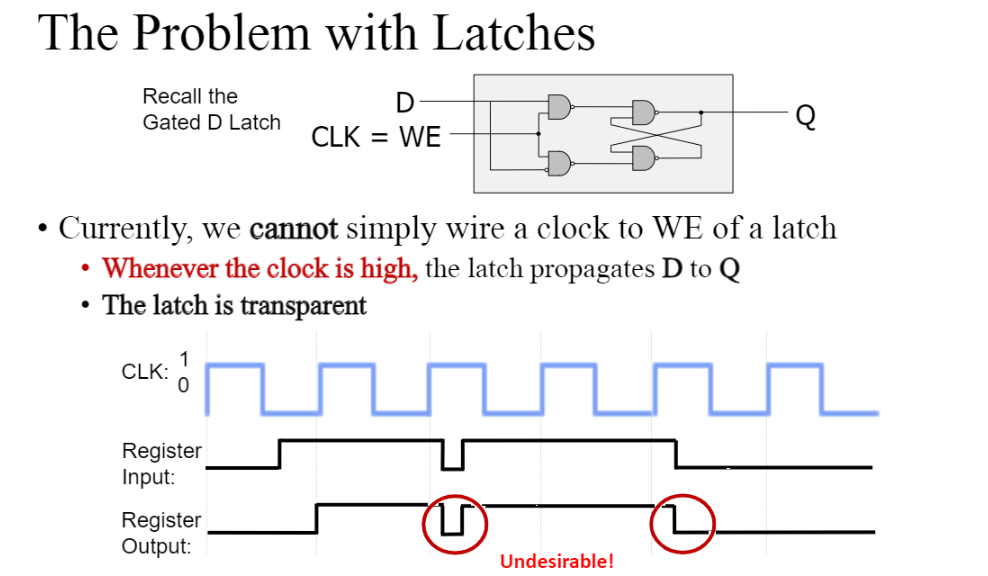

6) clock

- 반복적으로 0과 1로 값을 가지는데 clock을 통해 state를 바꿈

- 상태의 변화를 이끌어 내는 trigger임

- clock을 통해 각각이 언제 변하는지 동기화할 수 있음 -> 동기화가 되지 않는다면 굉장히 불안정함

- 조합회로의 최대 딜레이 시간에 맞춰서 clock cycle을 설정함

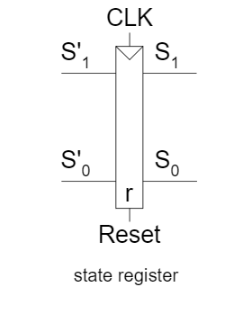

7) state resister의 구현을 위한 두가지 요구사항

- clock 사이클의 edge 부분, 즉 클럭이 변하는 시기에 데이터를 저장해야함

- 전체 clock 사이클 동안 데이터는 이용가능해야함

- input이 변경되더라도 clock의 엣지에서 output이 변경되어야하는데 그렇지 않음

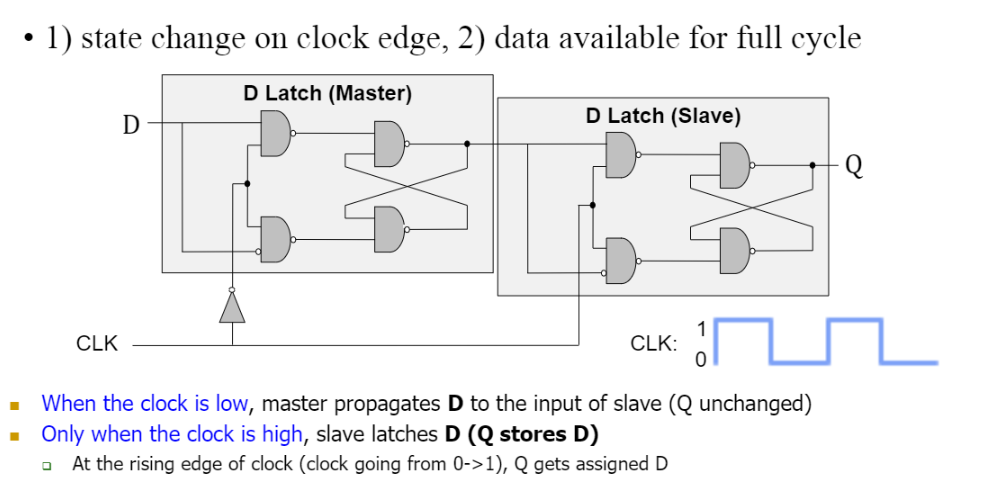

-> 이 문제를 해결한 새로운 element인 D Flip-Flop이 등장함

(1) D Flip-Flop

- D라는 값이 변경될 때 바로 Q의 값이 변경되는 것이 아닌 clock이 1이 되는 시점에 Q의 값이 변경됨

- D Flip-Flop을 활용한 레지스터를 만들 수 있음

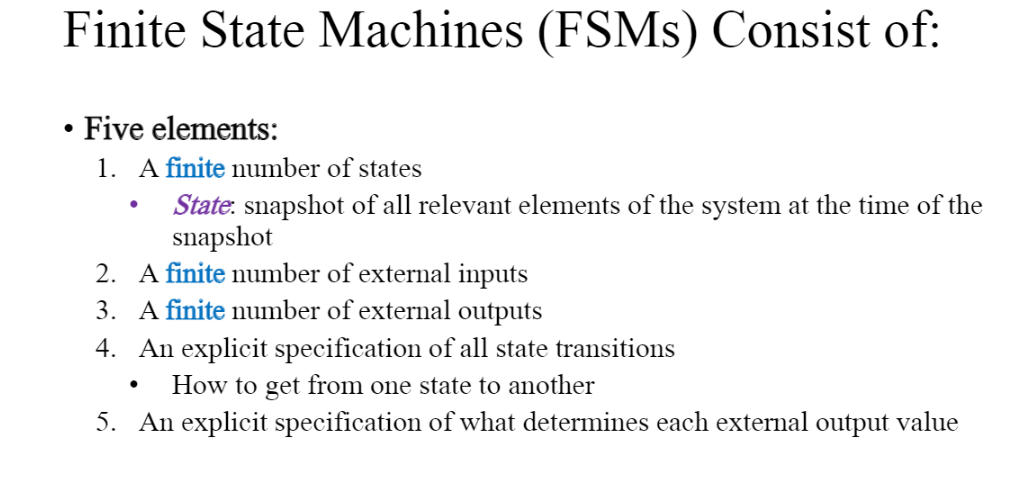

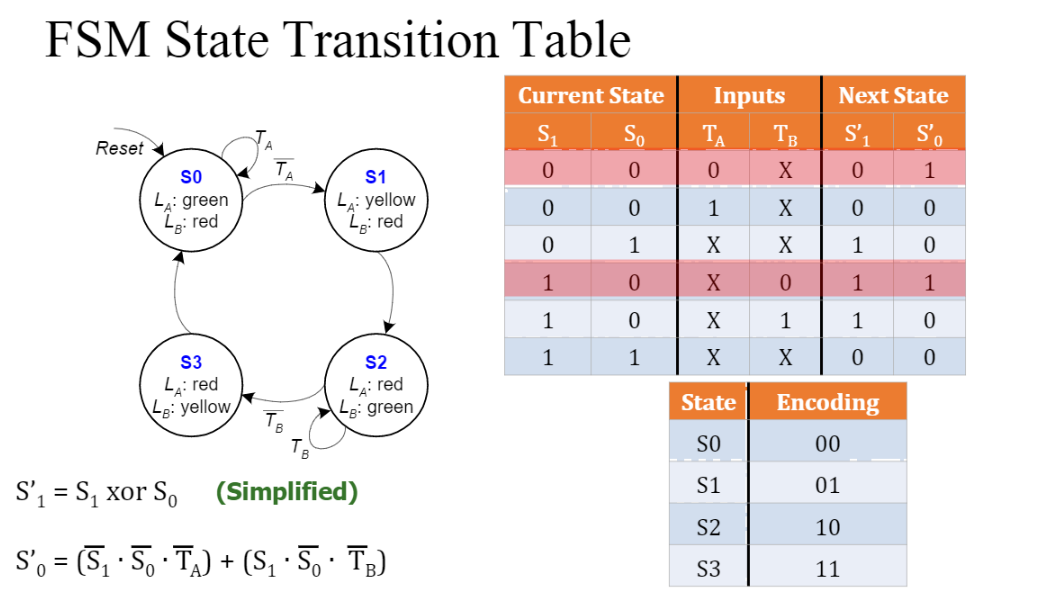

2. Finite State Machine(FSM)

1) 개념

- 상태가 있는 시스템에서 discrete한 모델

- 각각의 상태는 주어진 상황에서 시스템이 어떤 상태인지 나타냄

- 시스템이 될 수 있는 모든 가능한 상태를 그리고, 어떤 조건에서 상태를 변화하는지 나타낼 수 있음

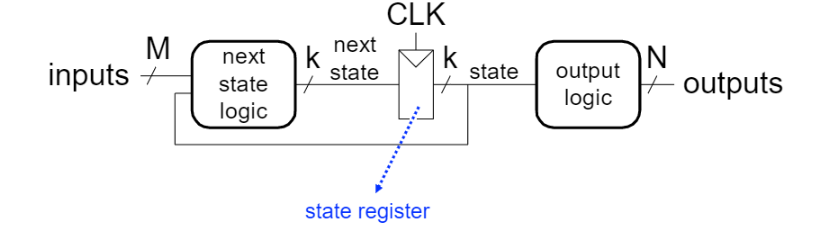

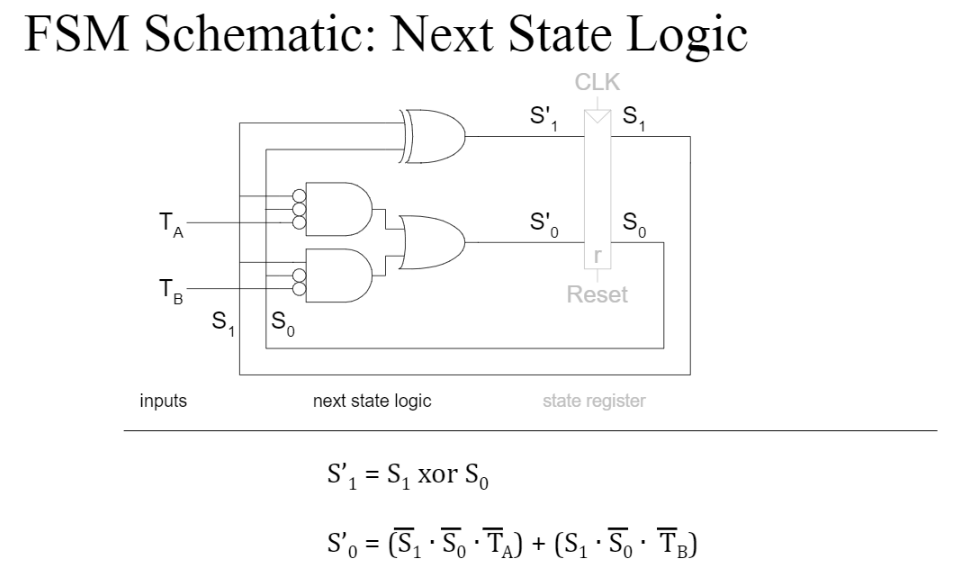

2) FSM의 세가지 파트

- next state logic

- state register

- output logic

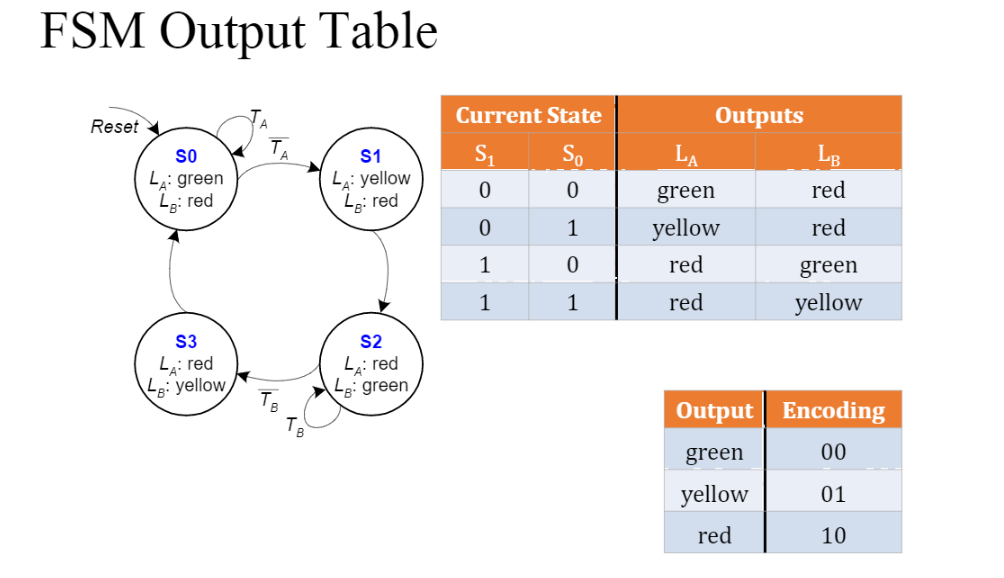

FSM 예제) 스마트한 신호등

- 차가 계속 다니는 경우 초록불을 계속 유지하도록 함

3. state bits 인코딩 방법

1) Fully Encoded

- 모든 상태에 대해 최소한의 비트를 통해 인코딩을 진행

ex) 00, 01, 10, 11

- Flip-Flop을 최소한으로 사용할 수 있음

2) One-Hot-Encoded

- 모든 상태만큼 비트를 만들어 하나의 비트가 각 state가 되도록 함

ex) 0001, 0010, 0100, 1000

- Flip-Flop을 최대한으로 사용하지만 디자인하기가 매우 간단하지만 비쌀 수 있음

3) Output Encoded

- 각 상태에 대한 output을 가지고 인코딩함

ex) 001, 010, 100, 110 -> 빨간불, 노란불, 초록불

4) Moore와 Mealy FSMs

- 결과는 동일하지만 구현하는 방법의 차이가 존재한다.

'강의 내용 정리 > 컴퓨터구조' 카테고리의 다른 글

| 컴퓨터 구조 (7), Pipelining (0) | 2022.05.23 |

|---|---|

| 컴퓨터 구조 (6), Single-cycle MIPS processor (0) | 2022.04.28 |

| 컴퓨터 구조 (5), Instruction Set Architecture 02 (0) | 2022.04.21 |

| 컴퓨터 구조 (2) Combinational Logical Circuits and Design (0) | 2022.03.15 |

| 컴퓨터 구조 (1) Computer Organization & Performance (0) | 2022.03.10 |